A reusable, easy configurable and user

advertisement

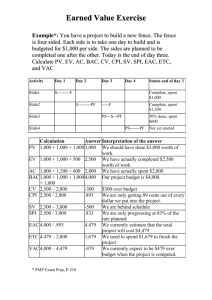

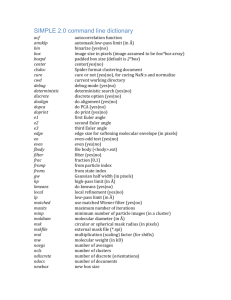

ABSTRACT This paper introduces a universal SPI UVM testbench, which can be easily reused in any ADI’s SPI project, even the SPI protocol is totally different. The only thing you need to do is filling an Excel configure file and running a command, then the customized SPI testbench will be automatically generated. This SPI UVM testbench also supports UVM register abstraction layer (RAL), which can be generated from yoda and easily updated. In order to make authoring testcases simple, three methods are supported: UVM sequences, tasks, or a configure file. The spi testbench structure and methodology can be extended to build other VIP (verification IP). BACKGROUND SPI is a duplex, synchronous, serial bus. It is wildly used in a lot of projects. But SPI is lack of a uniform protocol, it’s reflected in wide variety of protocol options. For each new project, the verification engineers need to develop a new testbench. As the design update, the testbench must be updated accordingly. It is a significant waste of time and resources. This SPI UVM testbench based on ADE9000 SPI design. ADE9000 is the next-gen 3 phase’s electricity meter chip. Since SPI is the most import interface for this project, other verification engineers will use SPI to read/write registers, memories in the top level verification. The design engineers and product test engineers will also build testcases. So there are three methods supported to make authoring testcases simple: UVM sequences, tasks, or a configure file. PROJECT DESCRIPTION This SPI UVM testbench has three highlighted aspects: 1. It can be reused in any ADI’s SPI project. 2. It can be easily configured by an Excel file based on different protocols. 3. It supports user-friendly tasks and configure file to build testcases. DESIGN 1. Figure 1 shows the structure of this SPI UVM testbench. It is a typical UVM based testbench, includes spi master agent, bus agent, scoreboard, register model, adapter and spi_cfg. The spi master agent is the most important component. It consists of sequencer(sqr), driver(drv) and monitor(mon). Sequencer gets transaction level packets from sequences, and sends them to driver, the driver converts transaction to actual simulation to SPI interface. The monitor can collect transaction from the interface. Use configure “ACTIVE” to choose if driver and sequencer are included. The scoreboard and bus agent is specific for ADE9000 project, they can be shared in ADE9000 top verification to check the SPI dut behavior, but they cannot be shared in other projects. So use a “spi_check_en” to switch if they are included. This testbench also support UVM register abstraction layer (RAL). The feature can be choose by “ral_en”. The register model can be updated by yoda, the adapter is used to convert between spi and register transaction. The spi_cfg defines parameters which can be configured for spi protocol and transaction. When run a testcase, it will upload parameter values from the configure file. For now only support XML and TXT format file. 2. Since SPI is lack of a uniform protocol, for different projects, usually the spi protocols are total different. This testbench prepares nearly all the possibility parameters to define a SPI protocol. These parameters includes number of address bits, data width, clock polarity, clock phase, operation type and other options. When the user reuse this testbench in a new project, the first thing to do is configuring the protocol. The user only need to fill an Excel configure file and running a command, then the customized SPI testbench will be automatically generated. In order to generate various testcases, there are many parameters supported. For example, SCLK frequency, duty cycle, missed clock cycle number, the delay between CSN and SCLK, and other parameters. 3. In order to make other users authoring testcases simple, there are three methods are supported: UVM sequences, tasks, or a configure file. UVM sequences is basic method to build UVM based testcases, It good at constraint randomize method. For the engineers who are not familiar with UVM can use the tasks or configure file to build testcases painless. The tasks support read, write and burst operations. To run the direct testcases, the user can use configure file method, he/she only need to fill the value of each parameter, no updated parameters will use the default value. cfg file SPI UVM TESTBENCH Heading spi_env spi_cfg spi_check_en ral_en Register model scoreboard adapter sequences spi_agent bus_agent sqr sqr ACTIVE drv mon mon drv spi_if bus_if DUT(SPI) Figure 1. Structure of SPI UVM testbench RESULTS This SPI UVM testbench has been used for ADE9000 SPI block level verification, and also be integrated in the top level verification. The reaction from other verification, design and test engineers who used this testbench was very good. They thought the tasks and configure file are quit user-friendly, they can build testcases very quickly. For now I tried to use this testbench to connect with ADE9002 and ADF7030 SPI, it works well and can generate expected simulation. CONCLUSION 1. This testbench can be shared in the ADE9000 top level verification. 2. This testbench can also be easily reused in other projects. 3. Good reflection from other engineers about user-friendly tasks and configure file. The spi testbench structure and methodology practices successful, it can be extended to build other VIP (verification IP).