60103_r02

advertisement

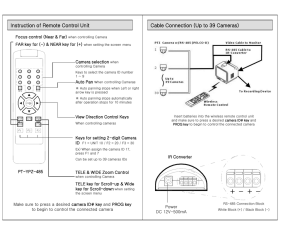

Rev. ECO Description Author Approved Date 01 37-218 Initial release ZKhan 11/Mar/2015 02 37-304 Updated for CDR ZKhan 28/July/2015 TESS Observatory Simulator Functional Description Dwg. No. 37-60103 Revision 02 28/July/2015 37-60103 i Revision 02 Table of Contents 1 Introduction ............................................................................................................. 1 2 Observatory Simulator Functions ......................................................................... 2 3 Observatory Simulator Description ...................................................................... 2 3.1 3.2 3.3 3.4 3.5 3.6 3.7 Block Diagram............................................................................................................ 2 Inputs .......................................................................................................................... 3 Outputs ....................................................................................................................... 3 Hardware Description ................................................................................................ 3 Firmware Description ................................................................................................ 4 Software Description ................................................................................................. 5 Data Handling Sequence ........................................................................................... 5 37-60103 ii Revision 02 Preface This is the TESS Observatory Simulator Functional Description. Revision 01 is the initial release for comment. Revision 02 is an update for CDR and includes details about software functions and the data handling sequence. 37-60103 iii Revision 02 1 Introduction The Observatory Simulator is a system to simulate the TESS Observatory during development of the TESS Instrument cameras. This document describes the interfaces and basic functions of the Observatory Simulator. The hardware, firmware and software of the Observatory Simulator system are also described in detail. Figure 1 shows the thermal vacuum (TVAC) test setup in which the simulator will be used. Tests may also be done with other test setups but the interfaces of the observatory simulator will remain the same. Note that the simulator can support testing of two cameras at a time. Figure 1 - Camera Test Setup 37-60103 1 Revision 02 2 Observatory Simulator Functions The Observatory Simulator supports the concurrent operation of two cameras during testing. The basic functions of the Observatory simulator are as follows: Receives commands from Camera Test Console Send responses [to commands] to Camera Test Console Sends commands to cameras o Program and configure camera Provides power to cameras o Includes survival mode heater power o Includes current monitoring Receives data from cameras: image and housekeeping Sends raw image data to Camera Test Console Send camera housekeeping data to Camera Test Console Generates its own time reference The Observatory simulator will use as much as possible of the flight DHU firmware. 3 Observatory Simulator Description 3.1 Block Diagram Figure 2 - Observatory Simulator Block Diagram 37-60103 2 Revision 02 Detailed Zynq board block diagram can be found in the board user guide: http://www.xilinx.com/support/documentation/boards_and_kits/zc702_zvik/ug850-zc702eval-bd.pdf 3.2 Inputs From Camera: Image data Housekeeping data – e.g. temperatures, voltages From Camera Test Console: 3.3 Simulator commands Outputs To Camera: Commands To Camera Test Console: Response to commands Camera image data Camera housekeeping data To Scope: 3.4 Current monitoring data (hardware) Hardware Description Zynq single board computer: o Kintex 7 board with Processor Programmable Logic 1 GB DDR RAM o Mezzanine card [Schematic in document number 37-60103.01]: Connectors to camera : power, data In-house design Two boards: 37-60103 Power adapter board : power connectors & switches & current monitoring 3 Revision 02 o Emulation adapter board: data connector – connected to zynq board 1G Ethernet port Observatory simulator housing Power supply o Operational power switch [on box] o Survival power switch [on box] o Includes current monitoring: Connectors on housing to output analog voltages scaled to 1V/Amp to allow monitoring of the current sources to the cameras. Output represents the sum of the current for both cameras for each supply voltage (+5,+15,-12). 3.5 Firmware Description Figure 3 Firmware Block Diagram Note that the Block RAM has 3 distinct blocks: 1 for commands going to the cameras, 1 for data/housekeeping from Camera A, 1 for data/housekeeping from Camera B. Other firmware functions: FPGA generates 1 PPS 37-60103 4 Revision 02 3.6 Software Description Software (in Processor) Interface to FPGA: Write commands over AXI to shared memory buffer A that FPGA reads Handle interrupt by FPGA: o Read shared memory buffer B over AXI to get camera image and housekeeping data Software (in Processor) Interface to Camera Test Console: Receive commands via User Datagram Protocol (UDP) port Process commands Generate command response to UDP port Software functions: Packetize images Add timestamps to images: images are tagged base on running number of frames requested from the camera. Image data is transferred in a UDP packet stream for reception by the Camera Test Console 3.7 Data Handling Sequence 1. (Optional) – If FPE is not programmed, a bit file can be transferred from the FPE's FPGA via the serial command interface. 2. Software in processor configures FPE Sequencer in Camera by sending commands to the Camera through the Command Interface in Programmable Logic 3. Software in processor sends a command to the Command Interface to enable generation of the 1 PPS. 4. Command Interface sends frame start to FPE in Camera. 5. When the frame start is successfully transmitted to the FPE, Data Image Interface sends frame start interrupt to Processor 6. Software in processor transmits a “Frame Start” UDP packet to the Camera Test Console. 7. Data Image Interface in Programmable Logic collects image data from Camera & writes it to Block RAM. 8. Data Image Interface sends image data interrupt to Processor 37-60103 5 Revision 02 9. Software in processor reads image data from Block RAM & writes it into DDR memory. 10. Software in processor reads image data from DDR memory and transmits it via a UDP port to the Camera Test Console. 11. Steps 7 through 10 are repeated till a full frame is accumulated in DDR memory. The data is also streamed out the UDP port to the Camera Test Console. Once the entire contents of the DDR memory have been transmitted it is reused for the next frame. 12. The software in processor waits for the next frame start interrupt from the Data Image Interface. While waiting, any remaining untransmitted data from the previous frame is sent on the UDP port to the Camera Test Console. If a new frame start arrives before transmission of previous frame is finished, the data in the DDR memory is discarded. In addition to the handling of image data in steps 4 to 12, housekeeping data is handled as follows: 1. Command Interface sends command to FPE in Camera to send housekeeping data back. 2. Data Image Interface in Programmable Logic collects housekeeping data from Camera & writes it to Block RAM. 3. Data Image Interface sends housekeeping data interrupt to Processor 4. Software in processor copies the housekeeping data from the Block RAM to a secondary buffer. 5. At the beginning of each image frame, the software in processor transmits a housekeeping data UDP packet containing the most recent housekeeping to the Camera Test Console. 37-60103 6 Revision 02