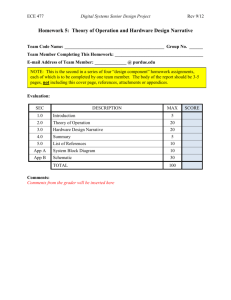

Lab 3

advertisement

CEC 222 Digital Electronics Lab Spring 2015 Lab 3: Basic Combinational Logic Circuits Learning Objectives: Introduction to determining logic behavior from a circuit. Analyze a word problem, designing and test a circuit realization of the solution. Reinforce the concept of minterms and maxterms. Lab Overview: When solving a digital logic problem there are often multiple valid solutions that appear quite different. The “best” solution may depend on which criteria you wish to optimize. In the pre-lab you will develop two valid solutions, for a majority voting problem, one via minterms and the other via maxterms. The lab consists of developing both solutions in the Xilinx ISE design environment as schematics, programming each into your FPGA, and recording the results. The extra credit experiment requires the development of a “simpler” solution to the majority voting problem that conforms to neither a SOP nor POS form. YOUR NAME(S) Lab 03 Page 1 of 10 CEC 222 Digital Electronics Lab Spring 2015 Pre-Lab (10%) Pre-Lab Part 1: The logic relationship between the inputs and the output(s) can be described by a logic circuit, a truth table, or a waveform. Task 1. Considering the simple logic circuit Figure 1 A simple logic circuit presented in Figure 1, wherein A, B, and C are inputs and F is the output, fill in the Intermediate Results and Output columns of Table 1. Table 1 Truth Table for Pre-Lab part 1 Intermediate Results Inputs A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Task 2. C 0 1 0 1 0 1 0 1 A AB AB ABC ABC Output AB ABC F Considering the logic circuit presented in Figure 1, draw the output waveform corresponding to the inputs given for A, B, and C. Figure 2 Waveform corresponding to a simple circuit. YOUR NAME(S) Lab 03 Page 2 of 10 CEC 222 Digital Electronics Lab Spring 2015 Pre-Lab Part 2: Three engineering students sharing a dorm room often argue about whether to have the television on or off. Finally, they concede to majority rule. Develop a “voting” circuit that sets the output HIGH if and only if the majority of the three inputs are high. Task 3. If the three students are represented by A, B, and C, fill in the “Pre-Lab” Output column of the truth table shown in Table 2 for the majority voting logic. The decision to have the television on or off is represented by the output F. Task 4. Sketch the output waveform to corresponding to the inputs given for A, B, and C in Figure 3. Figure 3 Waveform for majority voting circuit. Question 1. What is the minterm expansion for F (i.e., in canonical SOP form)? DO NOT SIMPLIFY!! F = m? + m? + … Task 5. On paper, or otherwise, “sketch” an AND / OR gate realization of your minterm expansion. Question 2. What is the maxterm expansion for F (i.e., in canonical POS form)? DO NOT SIMPLIFY!! F = M? M? … Task 6. On paper, or otherwise, “sketch” an OR / AND gate realization of your maxterm expansion. Be sure to bring these sketchs with you to the Lab. YOUR NAME(S) Lab 03 Page 3 of 10 CEC 222 Digital Electronics Lab Spring 2015 Experiments (90%) EXPERIMENT 1. THE MAJORITY VOTING CIRCUIT – MINTERM EXPANSION In this initial experiment you will be implementing the majority voting circuit that you designed in the prelab. In Experiment 1 you will build the minterm version of your majority voting circuit followed by the maxterm version in Experiment 2. Step 1.a: Create a new project with a blank schematic Open ISE1 and select File -> New Project. Enter “Majority_Minterm” in the Name: field. Be sure to select “Schematic” from the drop-down menu “Top-Level source type” and then click on the “Next” button. The “Project Setting” window which appears next, should be set as shown: Device: XC3S100E Package: CP132 Select “Next,” and then “Finish.” You should now have a new empty project!! In the top-left pane labeled “Hierarchy” right-click on “Majority_ Minterm” and select “New Source.” Select schematic for the source type and enter “Lab3_Experiment1” in the “File Name” field. Be sure that the “Add to project” box is selected and click on “Next” then “Finish.” You should have a blank schematic in preparation for building your circuit(s). Step 1.b: Build the minterm version of your majority voting circuit. 1 All Programs -> Xilinx Design Tools -> ISE Design Suite 14.7 -> ISE Design Tools -> 64-bit Project Navigator YOUR NAME(S) Lab 03 Page 4 of 10 CEC 222 Digital Electronics Lab Spring 2015 In the bottom left corner, click on the “Symbols” tab ( To add a gate to your schematic locate the appropriate name in the “Symbols” ). pane (left) and select it to highlight the name. For example, select “and3” to select a three input AND gate Move your cursor to the main schematic window and note that a shadow of the selected gate follows your cursor. Click once to place the gate in your schematic. Repeat this procedure to include additional gates to your design. Pressing “Esc” will end gate placement. Now you are ready to add wiring to connect your gates. From the vertical pane of icons select “Add Wire” (or from the “Add” pull-down menu select “Wire”). Click once on the first point to be connected and again at the destination point. Search “Drawing Wires with Automatic Routing” in ISE Help for more info. Again, press “Esc” to end wiring. To be able to bring input signals into your design and send output signals from your design, you will need to include input / output ports. From the vertical pane of icons select “Add I/O Marker” (or from the “Add” pull down menu select “I/O Marker”). Add three input ports and one output port (“Esc” to end). To rename the I/O ports select the pointer (Arrow icon), right click on any I/O Marker, and then select “Rename Port.” Enter a meaningful name such as A, B, C, for the inputs, and F for the output. Use the “Add Text” icon to label the intermediate signals, as shown in Figure 1. Double click on the default “Text Value” to change the Text Value. Set the “Text Font Size” to 36 and “Text Color” to red. Also add a schematic title, which includes your name, at the top of the schematic. Task 7. Take a screen shot of your schematic and insert it into Figure 4. Note that the neatness and clarity of your schematic account for a significant portion of your grade. YOUR NAME(S) Lab 03 Page 5 of 10 CEC 222 Digital Electronics Lab Spring 2015 Figure 4 Minterm Schematic of majority voting circuit Step 1.c: Route the signals (A, B, C, and F) to appropriate pins on the FPGA. Some of the pins on your Xilinx FPGA (the small chip in the center of your BASYS 2 board) have been connected, by Digilent, to things such as switches (SW7 to SW0), LEDs (LED7 to LED0), and I/O ports (e.g., JA, .., JD). To route the signals, you will need to create a User Configuration File (UCF). Click on the “Design” tab at the bottom left of the ISE window and then right-click on “Lab3_Experiment1” in the Hierarchy window. Select “New Source” and click on Implementation Constraints file. Enter “experiment1” for the “File name” then select “Next,” and then “Finish.” You will need to enter text into the empty “experiment1.ucf” file in order to route the signals: Input “A” to SW2 = FPGA pin K3 Input “B” to SW1 = FPGA pin L3 Input “C” to SW0 = FPGA pin P11 Output “F” to LED0 = FPGA pin M5 The UCF file from Lab2 Experiment3 is shown as an example. The “#” symbol precedes a comment. Be sure to save all of your files before continuing. YOUR NAME(S) Lab 03 Page 6 of 10 CEC 222 Digital Electronics Lab Spring 2015 Step 1.d: Generate the programming (i.e., *.bit) file. Select the bottom left tab and click on “Lab3_Experiment1.” In the pane below, double-click on “Synthesize” and in a few seconds the “?” ( should change to a tick mark ( ) ). If you have an error, the lower “Console” window will describe what is wrong. Fix the error and run Synthesize again. Similarly, double-click on “Implement Design” and in a few seconds the “?” should change to a tick mark. Finally, double-click on “Generate Programming File.” You have generated a “lab3_experiment1.bit” file that can now be loaded into your FPGA in order to realize your design. Step 1.e: Program the FPGA. Turn on your BASYS 2 FPGA board and start the Adept software Browse to the “lab3_experiment1.bit,” which you just created and load it into the PROM. After programming, you may need to turn the power to your FPGA board OFF and back ON in order to load the new design. Task 8. Vary the switches SW2 (=A), SW1 (=B), and SW0 (=C) to enter every possible combination of inputs and record the corresponding output (=F) values in the Minterm column of Table 2. EXPERIMENT 2. THE MAJORITY VOTING CIRCUIT – MAXTERM EXPANSION In Experiment 1, you built the minterm version of your majority voting circuit. In this second experiment, you will be implementing the maxterm version. Step 2.a: Create a new project with a blank schematic Open ISE and select File -> New Project. Enter “Majority_Maxterm” in the Name: field. Select “Next” and then “Finish.” In the top-left pane labeled “Hierarchy” right-click on “Majority_ Maxterm” and select “New Source.” YOUR NAME(S) Lab 03 Page 7 of 10 CEC 222 Digital Electronics Lab Spring 2015 Select schematic for the source type and enter “Lab3_Experiment2” in the “File Name” field. Continue with the same steps as you did before in Experiment #1 in order to create and load the “lab3_experiment2.bit” file. Task 9. Capture a screenshot of your maxterm schematic and inserte it into Figure 5. Figure 5 Maxterm schematic of the majority voting circuit. Task 10. Vary the switches SW2 (=A), SW1 (=B), and SW0 (=C) to enter every possible combination of inputs and record the corresponding output (=F) values in the Maxterm column of Table 2. YOUR NAME(S) Lab 03 Page 8 of 10 CEC 222 Digital Electronics Lab Spring 2015 Report Requirements Truth table to be completed - Last column is optional. Inputs A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Table 2 Truth Table for the Majority Circuit Output F F F F (Pre-Lab) (Minterm) (Maxterm) (Extra Credit) Question 3. If you had to build a thousand of these majority voting circuits for a living, would you choose the minterm design or the maxterm design – be sure to explain your answer. ___________________??? YOUR NAME(S) Lab 03 Page 9 of 10 CEC 222 Digital Electronics Lab Spring 2015 Optional Exercise(s) (+10% Extra Credit) EXPERIMENT 3. A SIMPLER MULTI-LEVEL SOLUTION The majority circuit can be implemented with only two 2-input AND gates and two 2-input OR gates (no inverters). Question 4. What is the Boolean expression for this “simpler” solution? F = ???? Step 3.a: Develop a schematic, implement, and test your “simpler” four gate multi-level solution Task 11. Capture a screenshot of your simpler schematic nd insert it into Figure 6. Figure 6 A four gate “simpler” schematic of the majority voting circuit. Task 12. Vary the switches SW2 (=A), SW1 (=B), and SW0 (=C) to enter every possible combination of inputs and record the corresponding Output (=F) values in the Extra Credit output column of Table 2. Reference Material APPENDIX A: XILINX ISE DESIGN SUITE INFORMATION [1] ISE Design Suite 14: Release Notes, Installation, and Licensing [2] General ISE Help [3] Xilinx ISE WebPACK Schematic Capture Tutorial YOUR NAME(S) Lab 03 Page 10 of 10