docx - Personal Pages Index

advertisement

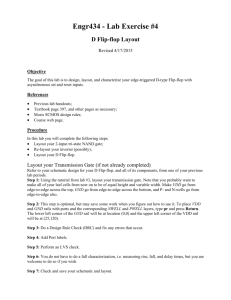

Engr434 - Lab Exercise #2 D Flip-flop Design Revised 4/8/2015 Name ____________________________ Score _________/20 Objective The goal of this lab is to do a design, create a schematic, and do timing characterization on several cells that can be used as components in a larger cell. References Lab #1 handout; Textbook, page 397, Figure 10.25; Mentor Graphics on-line help. Procedure In this lab, you are going to do a transistor-level design of an edge-triggered D flip-flop. To accomplish this task, you will start by designing and characterizing the smaller logic functions that can be stitched together to create the flip-flop. Rise times are measured from the 10% to the 90% level. Fall times are measured from the 90% to the 10% level. Delay times are measured at the 50% level. Characterize Your Inverter Step 1: Characterize one instance of your minimum-sized (width P/N = 5/2) inverter from Lab#1 by filling in the following (or copying the data from lab #1): Output fall time (ps): __________ Output rise time (ps): __________ Delay time, input rise to output fall (ps): __________ Delay time, input fall to output rise (ps): __________ Create a Transmission Gate Step 1: Create a transmission gate schematic and symbol (refer to your textbook for the schematic, and to the Lab#1 handout for the procedure). Step 2: Fill in the following information with the gate fully enabled: Output fall time (ps): __________ Output rise time (ps): __________ Delay time, input rise to output rise (ps): __________ Delay time, input fall to output fall (ps): __________ Create a 2-input NAND Gate Step 1: Create a 2-input NAND gate schematic and symbol. Step 2: Fill in the following information with one input enabled while the other input transitions: Output fall time (ps): __________ Output rise time (ps): __________ Delay time, input rise to output fall (ps): __________ Delay time, input fall to output rise (ps): __________ Create a 2-input Tristate NAND Gate Step 1: Create a 2-input Tristate NAND gate schematic and symbol (do a little research, be creative). Step 2: Fill in the following information with the gate enabled and one input enabled while the other input transitions: Output fall time (ps): __________ Output rise time (ps): __________ Delay time, input rise to output fall (ps): __________ Delay time, input fall to output rise (ps): __________ Create an Edge-Triggered D Flip-flop Step 1: Using the schematic in Figure 10.25 on page 397 of your textbook, create a schematic and symbol of an edge-triggered D Flip-flop with asynchronous set and reset inputs. Step 2: Fill in the following: Clock rising to Q rising (rising delay time) (ns): __________ Clock rising to Q falling (falling delay time) (ns): __________ Set to Q rising (ns): __________ Reset to Q falling (ns): __________ Maximum frequency achievable during simulation, calculated from delay times (MHz): __________ Step 3: Insert a 300fF (femto-farad) capacitor between the output and GND. The capacitor can be found in the adk_ic library. Fill in the following: Clock rising to Q rising (rising delay time) (ns): __________ Clock rising to Q falling (falling delay time) (ns): __________ Set to Q rising (ns): __________ Reset to Q falling (ns): __________ Maximum frequency achievable during simulation, calculated from the delay times (MHz): __________ To Turn in The following information is due at the start of class on Monday, April 13. Staple the following items together in the order presented below. Each person must turn in a complete set of documentation. This handout, with the numbers filled in appropriately; Schematic diagrams of your circuits. Include one page for each schematic, and one page for each symbol.