sampling_chip_4

advertisement

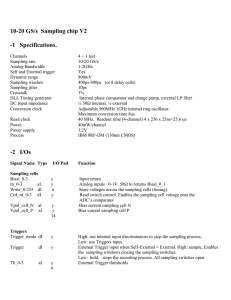

10-20 GS/s Sampling chip V4 -1 Specifications. Channels Sampling rate Analog Bandwidth Self or External trigger Dynamic range Sampling window Sampling jitter Crosstalk DLL Timing generator DC Input impedance Conversion clock 4 + 1 test + 1 timing 10-20 GS/s 1-2GHz 800mV 400ps-800ps (or 8 delay cells) 10ps 1% Internal phase comparator and charge pump, external LP filter ½ 50 internal, ½ external Adjustable 500MHz 1GHz internal ring oscillator. Maximum conversion time 8us. 40 MHz. Readout time (4-channel) 4 x 256 x 25ns=25.6 s 40mW/channel 1.2V IBM 8RF-DM (130nm CMOS) Read clock Power Power supply Process -2 I/Os Signal Name Type I/O Pad Sampling cells Biasl_0-5 In_0-5 Ctrl_rd aI aI dI Vpol_cell_N Vpol_cell_P aI aI Function Input return Analog inputs 0-1V, 50 to returns Biasl_0_1 Read switch control. Enables the sampling cell voltage onto the ADC’s comparator Bias current sampling cell N Bias current sampling cell P 15 Triggers TRIG_mode dI TRIG_ext TRIG_out_0-4 Trigger_or_out dI dI dO Th_0-4 aI 13 High: use internal input discriminators to stop the sampling process; Low: use External Trigger input External Trigger input active when Trigger mode low. Channel Triggers inputs. Or of the Channel Triggers outputs Low: hold, stops the recording process. All sampling switches open. External Channel Triggers thresholds Timing generator Write_ck write_ck VCN_in VCN_out VCP_in VCP_out vdl_out Pump_out ADC control Ramp_bias Ramp_buffer_bias Cext Ramp_buf_out freq_select clear_ADC ro_enable **Read_switch **Rp dI dI aI aO aI aO dO aIO 8 Write clock (40 MHz to timing generator) Copy of Write_ck Rising edge analog input control Rising edge analog output control Falling edge analog input control Falling edge analog output control Output from VCDL for delay lock Phase comparator up output aI aI aIO aO Ramp current analog control Ramp buffers current analog control External ramp input or internal ramp output (Vramp_out) Buffered Ramp output. dI dI dI Selects the ADC clock frequency (divide 1 or 4) Clears the ADC counters before conversion. RO buffers active. dI dI Ramp (Ramp) active low, high clears the ramp cap. 9 Read control Rd_ck-1-2 Tok_in-1-2 Tok out-1-2 Chan-decode-0-3 dI dI dO dI D0-11 d I dO Token-decode-1-3 dI Read clock (40 MHz) Input of the token passing Output of the token passing Channel address, selects the channel to be read. 0 no channel selected 1-5 channel 1-5 6 clear the ring oscillator monitor counter 7 xx (or channel 6 if implemented) 12-bit data bus controlled by the tokens (see below) and Chan-decode-03. Tied to ground in the Hi-Z state with a large internal resistor. Token control. Readout as 4 blocks of 64/channel (to skip known off-time data) 0 no block, 1-4 token block 1-4 5 clear token 6 clear trig 26 Power supplies Vdd +1.2V Gnd 0V Test structures Test ADC Analog_In_test Biasl_test Test_comp_out **Vpol_cell **Trig_test **Write_test **Samp_out **Ctrl_rd_test ro_monitor **Serial_DAT_test Comparator Comp_n Comp_p test_comp_out aI aI aO aI dI dI dO dI dO dO 10 Analog input 0-1V Input return Test comparator output Bias sampling cell Sample and Hold Write_test Sampling cell out (after buffer) Read sampling cell Buffered ADC clock output monitors (2 GHz/4096=500 kHz). aI aI aO 3 Test comparator input Test comparator input + Test comparator output Chip: 66 I/Os 36 Gnd 24 Vdd 126 pads Package CQFP120B: 120 pads All analog inputs protected with DC path to Gnd and Vdd +/- .6V (5 x 10 m2 diodes). -3 Operation Modes Modes -4 Write Writes continuously samples of inputs in a 60 fF sampling caps arrays at 10 GS/s for 25ns. Sampling stopped upon trigger. Convert Clears 2 GHz counter, ramps up Wilkinson ADCs for 2 s. Read Sequences 256 counters of the channel selected by Chan-0-3 onto the data bus at 40 MHz read clock rate. Readout can be partitioned into four blocks of 64 caps (token readout) for each channel. Token controlled by three bits (see above) Layout Blocks sizes: Timing generator Sampling cell Input comparator Comparator Counter Token Ramp Ramp buffer Ring Oscillator Divider 10 x 12 m2 12 x 100 30 x 25 12 x 30 12 x 300 12 x 40 100 x 300 260 x 65 12 x 50 12 x 300 x 256 “ x4 x 256 “ “ Size: 4500 x 4500 m2