Logic Design: NAND/NOR Gates, Complexity & Speed

advertisement

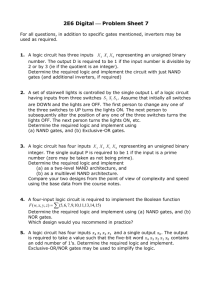

Lecture 7: Basic Logic Design In this lecture, we demonstrate how to apply our knowledge of Boolean algebra, expression minimisation, and basic gates to the design of relatively simple logic circuits. We also introduce two practical dimensions to the design problem: speed and complexity. Learning Outcomes: On completing this lecture, you will be able to: design a simple logic circuit from specification to implementation using NAND/NOR gates; investigate the possibility of a multilevel solution as distinct from a two-level sum-ofproducts or product-of-sums formulation; compute and assess complexity and speed metrics. 7.1 Logic Design Procedure We illustrate the steps involved in the design process by means of a worked example. Generally, a logic design problem begins with a verbal or functional statement of what the circuit is required to do. Example 7.1: A logic circuit has three inputs, labelled X2, X1, and X0. The single output, labelled F, is required to be 1 if a majority of the inputs are at 1. X2 X1 F X0 The first step in the design process is to convert the problem statement into a formal truth table: X2 0 0 0 0 1 1 1 1 X1 0 0 1 1 0 0 1 1 X0 0 1 0 1 0 1 0 1 F 0 0 0 1 0 1 1 1 The second step is to determine a simplified a Boolean expression for the required function. X1 1 X2 1 1 X0 7-1 1 The Karnaugh map step results in the equation F X 2 X1 X1 X 0 X 0 X 2 The next step is to give the corresponding logic diagram. Note that with the Boolean equation in sum-of-products form, the logic diagram comprises two levels of gates: a socalled level of AND gates, one for each product term, and an OR gate to realise the sum. X2 X1 X1 X0 F X0 X2 7.2 NAND Gate Constraint While it is clearly very convenient to implement the Boolean equation using the above AND/OR logic architecture, we have earlier noted that a better electrical performance might be derived from the use of NAND gates (or NOR gates). Thus the question arises: how might we convert the above logic diagram to one based as much as possible on the use of NAND gates? Recall from De Morgan’s laws that the NAND function can expressed: A.B A B If we sketch the corresponding logic diagrams for each side of the equation, we find that there are in effect two equivalent ways of representing the NAND gate: Now, noting that inserting two series inversions into a logic signal path does not disturb the overall logic function, we can amend our previous AND/OR logic diagram by adding two series inversions into each of the signal paths between AND output and OR input. In doing so, we in effect change each of the gates to a NAND gate. 7-2 X2 X1 X2 X1 X1 X0 X1 X0 F F X0 X2 X0 X2 The resulting logic circuit is termed a two-level NAND architecture. We see that any Boolean equation in sum-of-product form can be implemented with two levels of NAND gates. Additional inverters may be required if any of the inputs are required to be in complemented form. 7.3 Multilevel NAND Implementation The Karnaugh map gives a sum-of-product type of Boolean expression. Sometimes further grouping of common terms can produce a more simple implementation than that from the two levels of NAND gates. Consider, by way of example, the following Boolean function F ABC ABD ABC ABD The two level NAND implementation is shown as LCircuit V1. A B' C LCircuit V1 A B' D' F A' B C A' B D' Now, re-writing F in the form F ABC D ABC D leads to LCircuit V2 7-3 LCircuit V2 C' D A B' F A' B Further re-writing F gives F AB ABC D which in turn leads to LCircuit V3 A Lcircuit V3 B' A' B F C' D The circuits designated LCircuit V2 and V3 are said to be multilevel logic circuits they have more than the standard two levels of logic. A visual inspection of the three circuits would appear to reveal that V2 and V3 are simpler than V1 and that maybe even V3 is more simple than V2. However, what we clearly now require is a means for quantifying the complexity of the three designs. 7.4 Complexity/Area To put a measure on the complexity of a logic circuit what we basically need is an estimate of the silicon area the circuit will occupy when fabricated as an integrated circuit. Silicon area is taken up by active devices, ie transistors, and regions of metal required to interconnect the active devices. For the present discussion we will omit the interconnect area although for current integrated circuits interconnect area is becoming significant. Today’s standard integrated circuit technology is known as CMOS, standing for Complementary Metal Oxide Semiconductor, a form of field effect transistor. Since CMOS circuits are based solely on the use of transistors, and most of the transistors are made as small as the technology permits, a useful indicator of the area occupied is the number of transistors. For basic logic circuits, the following transistor counts (T) apply: 7-4 2T or 4T or 6T or 8T For every input, there are two transistors. Hence, comparing the three circuits of the previous section, we arrive at the following measures for the complexity: V1: V2: V3: (3 x 2T) + (4 x 6T) + (1 X 8T) = 38T (3 x 2T) + (1 x 4T) + (2 x 6T) + (1 x 4T) = 26T (3 x 2T) + (5 x 4T) + (1 x 2T) = 28T We indeed find that circuits V2 and V3 are simpler than V1 and that there is little difference between V2 and V3. 7.5 Delay/Speed Another very important specification for a logic circuit is its propagation delay t p, which in turn determines what is known as the switching or clock speed a quantity which is also frequently attached to a PC as a performance measure. VH Vi Vi t Vo VL VH Vo t VL tp The basic idea behind propagation delay is that, if the input changes state, the output also changes state with a small but finite delay; it literally takes the internal circuitry time to 7-5 respond to the changing input. If we consider the case of an inverter, we can represent the input/output situation with the above waveform diagram. The significance of tp is that, during tp, the logic circuit may be malfunctioning. In the case of the inverter, during tp, both the input and the output are in the same logic state so that the element is not functioning as an inverter. Thus, a key rule for a digital system is that significance must not be attached to a signal output until after the propagation delay has elapsed, thus delaying the next event in the system. Specific values for tp depend on the particular CMOS technology. Typical values for today’s technology would be as follows: 2 ns (ie nano-seconds, 10-9 s) or 2.5 ns or 3 ns or 3.5 ns Note that the delay increases with the number of inputs. Thus it is preferable to try to use gates having as few inputs as possible. Integrated circuit engineers do not normally employ gates having more than four inputs. Applying these measures to the circuit designs of section 7.3, and noting that delays add up as we proceed through logic levels, we arrive at the following worst-case delays: V1: V2: V3: tp = 3.0 + 3.5 = 6.5ns tp = 2.5 + 3.0 + 2.5 = 8.0ns tp = 2.5 + 2.5 + 2.5 + 2.0 = 9.5ns In this particular instance, the most complex circuit turns out to be the fastest (having the shortest delay). Of the circuits of roughly equal complexity, we see that V3 will have a small speed advantage. The example illustrates that in the design world, the engineer has to be clear about resolving conflicting design requirements; very often, the particular application will help in the resolution. 7-6 7.6 NOR Gate Implementation Again when confronting a design problem, it is often worthwhile to investigate as many solutions as possible. Thus far we have explored complexity and speed for NAND-based circuits. We now ask the question: can we convert a NAND-oriented design to a NOR implementation and work out its performance measures? By way of example, we return to the majority circuit of section 7.2 specified by the sum-ofproducts equation F X 2 X1 X1 X 0 X 0 X 2 The first step is to convert the equation to product-of-sums format. To do this, we form the Karnaugh map for the complement of F and minimise to get X1 1 X2 1 1 1 X0 F X 2 X1 X1 X 0 X 0 X 2 Complementing this via De Morgan to get back to F yields F X 2 X 1 X 1 X 0 X 0 X 2 X 2 X 1 X 1 X 0 X 0 X 2 X 2 X 1 X 1 X 0 X 0 X 2 Clearly this can readily be implemented as a two-level OR/AND logic architecture shown below. X2 X1 X2 X1 X1 X0 X1 X0 F X0 X2 X0 X2 7-7 F Again, De Morgan can be used to generate two alternative but equivalent forms of the NOR gate: A B A B Thus, adding in a pair of cancelling inverters in the above logic diagram for F allows the OR/AND architecture to be converted to a NOR only logic circuit. Again multilevel options can be explored and complexity and propagation delay measures determined for each design. 7.6 Conclusion In this lecture, we have illustrated the basic procedure for designing logic circuits: we go from formulation to truth table, to Karnaugh map, to Boolean equation, to implementation. We have treated both NAND and NOR forms of implementation, two levels of logic and multiple levels. We have introduced two quantitative means for comparing competing designs: complexity and overall propagation delay. We now go on to examine a number of important standard logic functions. 7-8