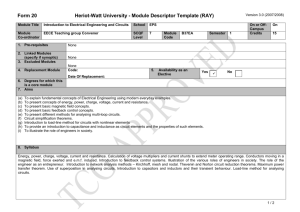

Dissertation Proposal - index

advertisement