A Low-Complexity Multiple Error Correcting Architecture Using

advertisement

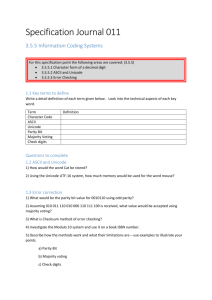

A Low-Complexity Multiple Error Correcting Architecture Using Novel Cross Parity Codes Over GF(2m) Abstract: This paper presents a novel low-complexity cross parity code, with a wide range of multiple bit error correction capability at a lower overhead, for improving the reliability in circuits over GF(2m). For an m input circuit, the proposed scheme can correct m ≤ Dw ≤ 3m/2 −1 multiple error combinations out of all the possible 2m − 1 errors, which is superior to many existing approaches. From the mathematical and practical evaluations, the best case error correction is m/2 bit errors. Tests on 80-bit parallel and, for the first time, on 163-bit Federal Information Processing Standard/National Institute of Standards and Technology (FIPS/NIST) standard word-level Galois field (GF) multipliers, suggest that it requires only 106% and 170% area overheads, respectively, which is lower than the existing approaches, while error injectionbased behavioral analysis demonstrates its wider error correction capability. Existing Method: A single error correcting architecture based on Hamming/low-density parity-check codes. However, this scheme cannot address multiple errors. There are also techniques, such as implication-based error detection. Implications exist in any circuit and their violations can be Interpreted as the occurrence of an error. A multiple error correction scheme for finite field arithmetic circuits has been proposed. While this scheme can correct multiple bit errors, it is suitable in applications where area is not a prime concern. Concurrent error correcting schemes specific to systolic polynomial basis and shifted dual basis multipliers are proposed. These schemes cannot be scaled to other architectures directly. a concurrent error correction scheme for type-t systolic Gaussian normal basis multiplier is proposed. In this scheme, error detection uses time redundancy and is specific to systolic type structures. The techniques are also designdependent error tolerant schemes. In addition, most of the cryptographic coprocessors rely Further Details Contact: A Vinay 9030333433, 08772261612 Email: takeoffstudentprojects@gmail.com | www.takeoffprojects.com heavily on one or more highly complex Galois field (GF) multiplier circuits, which can be a key target of an attacker. Proposed Method: This paper proposes a multiple error correction scheme for electronic circuits based on novel cross parity codes that provide a wide range of error correction capability. The sources of errors can be transient attacks and manufacturing faults causing multiple bit flips at the outputs. The scheme can be scaled to any architecture and can operate at lower area and power overheads compared with the existing approaches. this paper includes a novel cross parity algorithm for multiple error correction using the error detection features of the Bose–Choudhury– Hocquenghem (BCH) codes cross coupled with output parity prediction. The proposed technique corrects a wide range of multiple errors with acceptable area overhead, and comprises a novel decoding architecture for multiple error correction. Applications: 1) Bank automated teller machines. 2) Mobile communications. 3) Security….etc.. Advantages: Lower area and power overheads compared to other architectures. System Configuration:In the hardware part a normal computer where Xilinx ISE 14.3 software can be easily operated is required, i.e., with a minimum system configuration Further Details Contact: A Vinay 9030333433, 08772261612 Email: takeoffstudentprojects@gmail.com | www.takeoffprojects.com HARDWARE REQUIREMENT Processor Pentium –III - Speed - 1.1 GHz RAM - 1 GB (min) Hard Disk - 40 GB Floppy Drive - 1.44 MB Key Board - Standard Windows Keyboard Mouse - Two or Three Button Mouse Monitor - SVGA SOFTWARE REQUIREMENTS Operating System :Windows95/98/2000/XP/Windows7 Front End : Modelsim 6.3 for Debugging and Xilinx 14.3 for Synthesis and Hard Ware Implementation This software’s where Verilog source code can be used for design implementation. Further Details Contact: A Vinay 9030333433, 08772261612 Email: takeoffstudentprojects@gmail.com | www.takeoffprojects.com