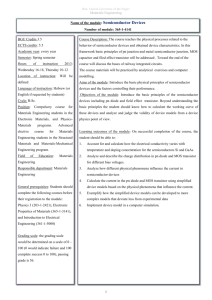

CONFERENCE AT A GLANCE

advertisement