Lab 10: D Flip

advertisement

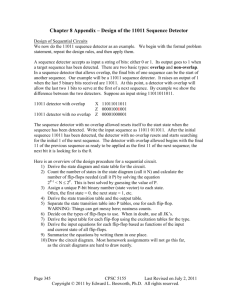

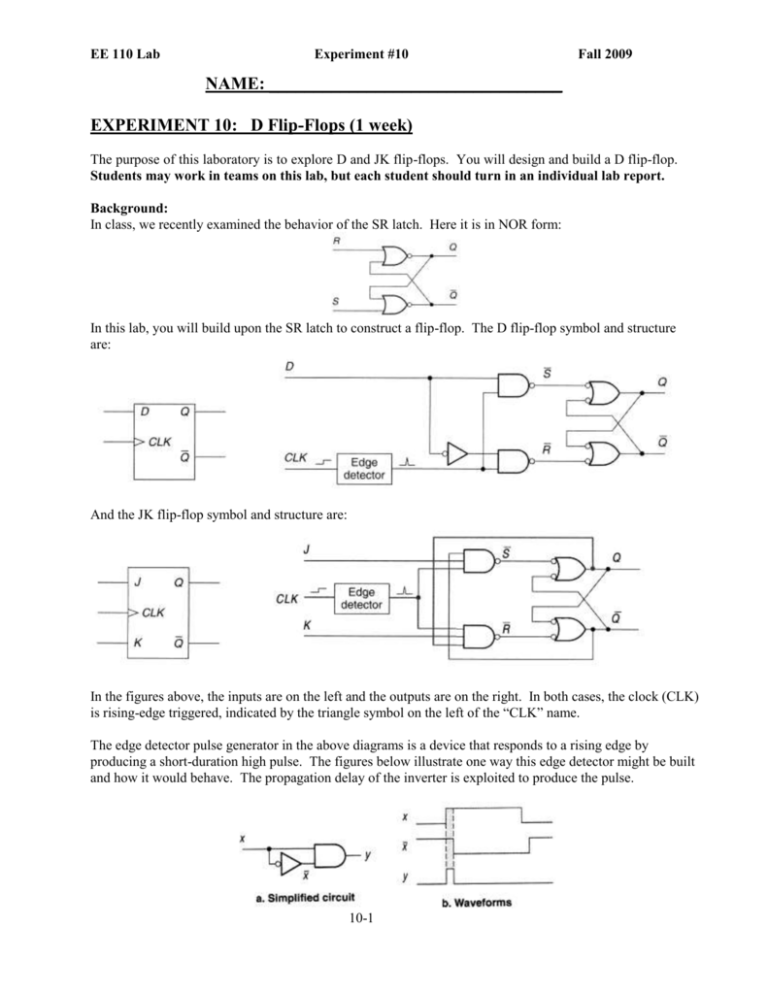

EE 110 Lab Experiment #10 Fall 2009 NAME: _________________________________ EXPERIMENT 10: D Flip-Flops (1 week) The purpose of this laboratory is to explore D and JK flip-flops. You will design and build a D flip-flop. Students may work in teams on this lab, but each student should turn in an individual lab report. Background: In class, we recently examined the behavior of the SR latch. Here it is in NOR form: In this lab, you will build upon the SR latch to construct a flip-flop. The D flip-flop symbol and structure are: And the JK flip-flop symbol and structure are: In the figures above, the inputs are on the left and the outputs are on the right. In both cases, the clock (CLK) is rising-edge triggered, indicated by the triangle symbol on the left of the “CLK” name. The edge detector pulse generator in the above diagrams is a device that responds to a rising edge by producing a short-duration high pulse. The figures below illustrate one way this edge detector might be built and how it would behave. The propagation delay of the inverter is exploited to produce the pulse. 10-1 EE 110 Lab Experiment #10 Fall 2009 NOTE: The single inverter stage as shown may not provide enough delay to produce a pulse long enough to operate the flip-flops correctly. I recommend that you use a cascade of three or five inverter stages. Pre-Lab: 1) Design an edge detector circuit similar to the one shown above. Be sure to use an odd number of inverter stages! I suggest you use the pulse switch to produce your input signal. Buffer the output of the pulse switch before sending it on to the edge detector’s cascade of inverters. Buffering the output means to send it through a gate or series of gates (for example, two inverters) to de-bounce the signal. The pulse switches are noisy; the switchcontacts don’t make a constant connection and the signal ‘bounces’. Sending the output of the pulse switch through two inverters or an AND (with other input HIGH) or OR (with other input LOW) will ‘de-bounce’ the output. 2) Draw the logic diagram of the edge detector circuit in the space below. Include pin numbers. Figure 1: Logic diagram of edge detector pulse generator. 3) Now, draw a schematic of the complete D flip-flop as you intend to build it. Feel free to use DeMorgan’s theorem to transform the OR gates to AND gates, if you wish. Use the edge detector circuit you designed above. Include pin numbers. 10-2 EE 110 Lab Experiment #10 Fall 2009 Figure 2: Schematic of D flip-flop to be built. Lab Procedure: 1) Build and test the edge detector stage you designed in step 1 of the pre-lab. Use the oscilloscope to observe the behavior and measure the duration (high time) of the pulse resulting from a rising edge input. Make sure you use enough inverter stages to produce an output pulse of at least 20 nanoseconds. You may need to add another two inverters to your edge detector to achieve a sufficiently long output pulse. Draw the logic diagram of the circuit in the space below to reflect exactly how you built the edge detector circuit. Figure 3: Logic diagram of edge detector pulse generator as built. 2) Draw a timing diagram below showing the behavior of your edge detector. Label the pulse width with the duration amount you measured. Figure 4: Timing diagram of edge detector pulse generator, showing one full cycle. 3) If your edge detector circuit in Figure 3 differs from your edge detector circuit in Figure 1, redraw your schematic (logic diagram) of the complete D flip-flop to include the edge detector 10-3 EE 110 Lab Experiment #10 Fall 2009 circuit that you actually built and tested in Figure 3. Otherwise, refer to your Figure 2 to build your D flip-flop. Figure 5: Revised schematic of D flip-flop to be built, using edge detector circuit as built. 4) Build the D flip-flop as you have designed it in Figure 5. 5) Test your D flip-flop circuit and complete the following truth table according to what you observe. Notice that you should exercise both the 0 and 1 states of the CLK input as well as its rising () and falling () edges. Q represents the initial state of the output. Q* represents what Q becomes when the specified stimulus is applied. Tilde (~) represents the complement operation. CLK D Present State Q 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 10-4 Observed Next State Q* ~Q* EE 110 Lab Experiment #10 0 1 1 Fall 2009 1 0 1 6) Demonstrate the operation of your circuit to the teaching assistant or professor. Get their signature and comments regarding the functionality of your circuits. TA Signature: _______________________________________________________________ 7) Complete the following: a. What results did you obtain in this experiment? b. What difficulties did you have? c. What are your conclusions? What did you learn about flip-flops? 8) J-K Flip-flop: Without building the JK flip-flop, complete the truth table on the next page, according to the behavior you would expect of it. The first eight cases involve the CLK behaving as a steady low, a steady high, or a falling edge. The rest involve the CLK rising edge. 10-5 EE 110 Lab Experiment #10 Present State CLK J K Q 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 10-6 Fall 2009 Predicted Next State Q* ~Q*