Test 2A Solutions

advertisement

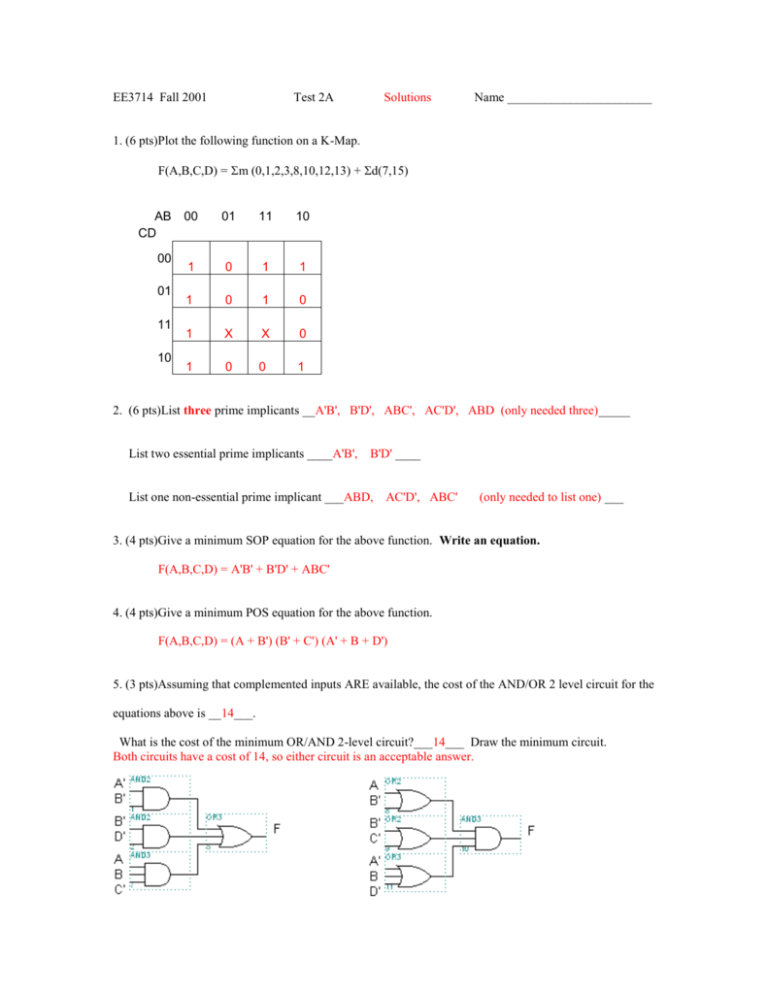

EE3714 Fall 2001 Test 2A Solutions Name _______________________ 1. (6 pts)Plot the following function on a K-Map. F(A,B,C,D) = m (0,1,2,3,8,10,12,13) + d(7,15) AB CD 00 01 11 10 00 01 11 10 1 0 1 1 1 0 1 0 1 X X 0 1 0 0 1 2. (6 pts)List three prime implicants __A'B', B'D', ABC', AC'D', ABD (only needed three)_____ List two essential prime implicants ____A'B', B'D' ____ List one non-essential prime implicant ___ABD, AC'D', ABC' (only needed to list one) ___ 3. (4 pts)Give a minimum SOP equation for the above function. Write an equation. F(A,B,C,D) = A'B' + B'D' + ABC' 4. (4 pts)Give a minimum POS equation for the above function. F(A,B,C,D) = (A + B') (B' + C') (A' + B + D') 5. (3 pts)Assuming that complemented inputs ARE available, the cost of the AND/OR 2 level circuit for the equations above is __14___. What is the cost of the minimum OR/AND 2-level circuit?___14___ Draw the minimum circuit. Both circuits have a cost of 14, so either circuit is an acceptable answer. 6.(4 pts)Write the following equation in SOP form. Do not minimize. F(A,B,C,D) = (AB) + (BD) + (CD) = A'B + AB' + BD + B'D' + CD' + C'D These are the symbols for exclusive OR (XOR) and exclusive NOR (XNOR) 7. (6 pts)Why is a NOR gate a complete logic family by itself? Show that it is able to implement all functions. To be a complete logic family, a family of gates must be able to implement an AND, an OR and a NOT function. 8. (8 pts)Put F= A’B + A’CD’ in NAND/NAND form. F(A,B,C,D) = F'' = [A'B + (A'CD')]" = [(A'B)' (A'CD')']' Put F= A’B + A’C’D’ in NOR/OR form. F(A,B,C,D) = [ (A'B )'' + (A'C'D' )'' ] = (A + B' )' + (A + C + D)' 9. (2 pts)The minimum POS form can always be found by complementing the minimum SOP form and using DeMorgan’s laws (true or false). False 10. (9 pts)What is a PLD? ____programmable logic device______ What is a PAL? ____programmable array logic________ What is a PLA? ____programmable logic array________ What is the difference between PALs and PLAs?__PALs have fixed OR planes; PLAs have programmable OR planes_ What is a FPGA? __field programmable gate array_____ Is a MUX programmable? ___no_____ What is the general equation for a MUX? Draw one showing inputs and output. F = S'Io + SI1 I0 I1 S 11.(10 pts)Mark the following diagram for the following 2 equations. Indicate which type of PLD is being used. F1(x1,x2,x3,x4) = x1x2x3’ + x1x2’ This is a PAL (The Or inputs are fixed) F2(x1,x2,x3,x4) = x1x2x3’ + x1’x4’ 11b.(10 pts)Mark the following diagram for the following 2 equations. Indicate which type of PLD is being used. F1(x1,x2,x3,x4) = x1x2x3’ + x1x2’ F2(x1,x2,x3,x4) = x1x2x3’ + x1’x4’ f1 This is a PLA (the OR plane is programmable) f2 12.(10 pts)Implement the following function using 2-input NAND gates. Write the equation. Draw the circuit assuming complemented input variables are not available F(x1,x2,x3) = x1x2x3’ + x1x2’ To use 2-input gates for the first term requires separating the term into two F = (x1x2)x3' + x1x2' Complementing the equation twice does not change the functionality. F = [(x1x2)x3' + x1x2']'' Using DeMorgan's law, F = [[(x1x2)x3']' [x1x2']']' Complementing the first AND gate twice allows the use of NANDs without changing the functionality. F = [[(x1x2)''x3']' [x1x2']']' The problem can also be solved by minimizing the equation. F = x1(x2x3' + x2') = x1(x3' + x2') = x1x3' + x1x2' = [x1x3' + x1x2']'' = [(x1x3')' (x1x2')']' This equation can now be implemented with 3 2-input NAND gates. 13.(2 pts)The values stored in a lookup table are the same as the __truth table values______ of the input variables. Also accepted output, function, truth table 14. (4 pts)To implement 8 different functions, with 4 different input variables (A,B,C,D), I need a memory device of size __24 = 16__locations X ___8___bits per location 15.(2 pts)Why is a memory device inefficient in implementing equations that have different input variables? When different input variables are used in implementing equations with a memory device, many locations have invalid data. Therefore there is a lot of wasted space. 16. (10 pts)Use Shannon’s expansion to expand the function F in terms of C. Use three 2:1 multiplexers to implement. F(A,B,C) = BC’ + AB’ C must be in each product term as either C or C'. It is not in the last product term so multiply by 1 (C + C'). F = BC' + AB' (C + C') Multiplying through F = BC' + AB'C + AB'C' Grouping common C terms together F = C' (B + AB') + C(AB') These are the inputs into the last MUX. A 1 B F A C 0 B