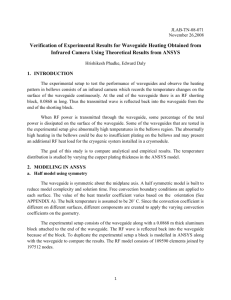

SP2 Shallow-ridge Waveguide

advertisement

Waveguide High-Speed Circuits and Systems Laboratory B.M.Yu High-Speed Circuits and Systems Laboratory 1 Content 1. Overview 2. Introduction 3. Design and fabrication I. Simulation II. measurement 4. Waveguide loss measurement 5. Coupling between shallow-ridge and narrow strip 6. Conclusion High-Speed Circuits and Systems Laboratory 2 Overview Optics Express (2010), Low Loss Shallow-Ridge Silicon Waveguide, Po Dong 2 um 0.25 um 3 um Cross section of WG Buried Oxide: 3 um, Cross section of waveguide: 0.25 um x 2 um Target : Chip to Chip interconnect (a few tens of centimeter) Average propagation loss: 0.274±0.008 dB/cm in C-band (1530~1565 nm) Double-level taper: to adiabatically couple from shallow ridge to strip waveguide High-Speed Circuits and Systems Laboratory 3 Introduction Silicon photonics: interest area for broad spectrum applications (optical interconnect, sensing, RF photonics) Submicron wide deeply etched waveguide structures - Efficient and high speed active photonic devices - SOI substrates (Top silicon thickness: 0.25 um) - Lowest propagation loss (in previous reports): 1~2 dB/cm @ 1550 nm - Chip to Chip interconnect & Narrow bandwidth filters in RF photonics Shallow ridge or thin silicon waveguide - Propagation loss: 0.3~1 dB/cm (selective oxidation fabrication technique) - Difficult to control (device density, hard mask thickness, cross section of WG) In this paper - Low loss silicon ridge WG: 0.25 um silicon, average propagation loss: 0.274 dB/cm High-Speed Circuits and Systems Laboratory 4 Design and Fabrication Simulation - Main reason of waveguide propagation loss: light scattering from etch sidewalls Minimizing optical field overlap with etched interface (increasing width of WG, decreasing etch depth) - Cross section of wave guide: 2 um x 0.25 um (etch depth: 0.05 um) - Power confinement: 84 % Etch sidewall of WG Shallow-ridge WG High-Speed Circuits and Systems Laboratory 5 Design and Fabrication Simulation Group index: ~3.7, effective index: ~2.9 - Etch depth tolerance ±0.01 um - Group index variation: 0.0033 5ps delay time difference (50cm waveguide) 40Gbps with a reasonable fabrication tolerance High-Speed Circuits and Systems Laboratory 6 Design and Fabrication Simulation bending loss with various bending radii Bending loss - 90° bending with various radii (50~120 um) - @ 100um radii 10-4dB High-Speed Circuits and Systems Laboratory 7 Design and Fabrication Fabrication 6 mm 3 mm SEM image of WG cross section Top-view of 64 cm waveguide - Soitec 6” wafers - 0.25 um thick silicon 3um buried oxide - Spiral waveguide (rmin= 300 um) - 6 mm x 3 mm waveguide (length of waveguide: 64cm) High-Speed Circuits and Systems Laboratory 8 Waveguide loss measurement Test setup Optical fiber (TE mode Polarization) ASE (𝜆 =1550 nm) Waveguide (horizontal taper) Optical fiber Optical spectrum analyzer High-Speed Circuits and Systems Laboratory 9 Waveguide loss measurement Loss measurement Insertion loss measured for different WG length as a function of wavelength Waveguide propagation loss using linear fitting @ 𝜆 =1550 nm - Insertion loss is normalized to power measured from direct to direct fiber coupling - Insertion loss = waveguide propagation loss + coupling loss - Waveguide loss: 0.281dB/cm (@ 𝜆 =1550 nm) High-Speed Circuits and Systems Laboratory 10 Waveguide loss measurement Loss measurement Waveguide propagation loss as a function of wavelength in C-band Waveguide loss with 9 chip on the same 6” SOI wafer - Average loss (𝜆 variation): 0.274 dB/cm ± 0.008 dB/cm - Same wafer but different average loss etch depth variation - Average loss (same wafer): 0.299 dB/cm High-Speed Circuits and Systems Laboratory 11 Coupling between shallow-ridge and narrow strip WG Double level taper Coupling between shallow-ridge and narrow strip waveguide 3-D simulation result - Narrow strip WG (450 nm x 250 nm): 1.5 um bending radius - In Ring modulator, narrow strip WG is more efficient. - Coupling would be need High-Speed Circuits and Systems Laboratory 12 Coupling between shallow-ridge and narrow strip WG Simulation result Coupling loss as a function of taper length - 10um long taper is sufficient in order to achieve <0.25 dB coupling loss - Highly index contrast between silicon and oxide High-Speed Circuits and Systems Laboratory 13