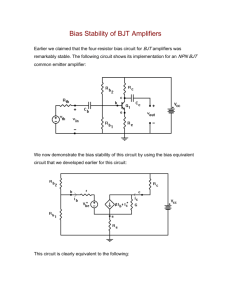

Section 5.5 Biasing of BJT Amplifier circuit

advertisement

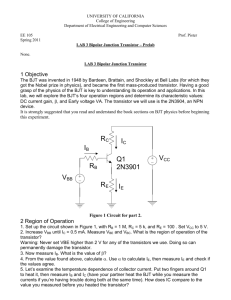

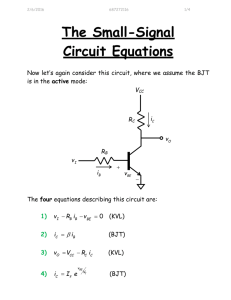

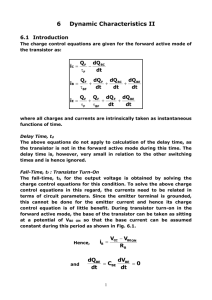

Section 5.5 Biasing of BJT Amplifier circuit Biasing of BJT Amplifier circuit • Biasing to establish constant DC Collector current Ic & should be • • • • Calculatable Predictable Insensitive to temp. variations Insensitive to large variations in β – To allow max. output signal swing with no distortion Figure 5.43 Two obvious schemes for biasing the BJT: (a) by fixing VBE; (b) by fixing IB. Figure 5.44 Classical biasing for BJTs using a single power supply: • Typical Biasing – Single power supply – Voltage Divider Network – RE in Emitter Circuit Typical Biasing R2 VBB VCC R1 R2 R1 R2 RB R1 R2 Figure 5.44 Classical biasing for BJTs using a single power supply: Classical Discrete-circuit Bias arrangement (a) I C I S e v BE VT Any variation in v BE , IC changes (b) iC i i changes iC Base Emitter Loop VBB I B RB VBE I E RE IE IB 1 RB I E RE VBB VBE 1 VBB VBE IE RB RE 1 Classical Discrete-circuit Bias arrangement • For stable Ic, IE must be stable as IC =αIE • To make IE insensitive to VBE (temp.) & β variations VBB VBE IE R RE B 1 VBB >> VBE RE>> RB/(β+1) Classical Discrete-circuit Bias arrangement VBB >> VBE For higher VBB at given V CC VRB2 VRB1 VRB1 VRC VCB For smallerVRB1 VRC smaller But for higher gain VRC should be more Larger signal Swing (before cutoff) Av=-VRC / VT VCB be large VCE is large for larger signed swing (before saturation) Compromise Role of thumb 1 VBB VCC 3 1 VCE or VCB VCC 3 1 I C RC VCC 3 Classical Discrete-circuit Bias arrangement RE>> RB/(β+1) For RE RB 1 - RB be small, thuslower value of R 1 & R 2 resultsin large current drain from thepower supply - Results in lower input impedanceof Amplifier- T hus LoadingEffect T radeoff Current through R c & R 2 I E - 0.1IE For Stable IE - Negative Feed Back through RE If IE increases somehow, VRE increases, hence VE increases correspondingly, VBB = VBE + VE ; VBE decreases for maintaining constant VBB Reduces collector (Emitter) current. Stable IE Figure 5.45 Biasing the BJT using two power supplies. Two Power Supplies Version For independent biasing R B can be eleminated, if signal is not applied to theBase & Base connectedto ground Two Power Supplies Version Base Emitter Loop I B RB VBE I E RE VEE IB IE 1 I B RB VBE I E RE VEE IE VEE VBE R RE B 1 VEE VBE RB RE 1 Figure 5.46 (a) A common-emitter transistor amplifier biased by a feedback resistor RB. A common-emitter transistor amplifier biased by a feedback resistor RB. Biasing using collector- Base Feed Back Resistor CommonEmitterconfiguration only RB provide negative Feedback A common-emitter transistor amplifier biased by a feedback resistor RB. I E IC I B VCC I E RC I B RB VBE IB IE 1 VCC VBE IE RB RC 1 VCC VBE RB RC 1 A common-emitter transistor amplifier biased by a feedback resistor RB. RB RC 1 VCB I E RB I B RB 1 RB Det erminessignal swing at t hecollect or. RB small Signal swing will be t hesmall. Input resist ancewill be small Loading A BJT biased using a constant-current source I. Biasing using a constant current source • Current in Emitter means – Constant IC IC =α IE – Independent of RB & β value thus RB can be made large to • Increase Input resistance • Large signal swing at collector •Q1 acts as Diode CBJ is short circuits Biasing using a constant current source Q1 acts as Diode CBJ is short circuits VCC-IREFR-VBE+VEE=0 I = IREF=(VCC-VBE+VEE)/R Since Q1 & Q2 have VBE is same I constant till Q2 in Active Mode (Region) & can be guaranteed by –Voltage at collector V > (-VEE+VBE) Current Mirror Biasing using a constant current source • IE is independent of β & RB • RB can be made large thus increasing input resistance • Simple Design • Q1 & Q2 are matched pair • Q1 is Diode collector- Base connected • β high IB can be neglected α = 1 IC = IE I = IREF=(VCC-VBE+VEE)/R