8051 Microcontroller Hardware & Intel HEX File

advertisement

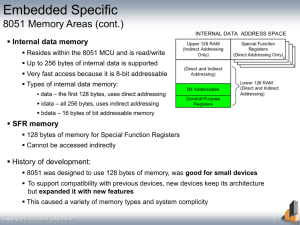

The 8051 Microcontroller and Embedded Systems CHAPTER 8 8051 HARDWARE CONNECTION AND INTEL HEX FILE 1 OBJECTIVES 2 Explain the purpose of each pin of the 8051 microcontroller Show the hardware connection of the 8051 chip Explain how to design an 8051-based system Explain the Intel hex file SECTION 8.1: PIN DESCRIPTION OF THE 8051 3 SECTION 8.1: PIN DESCRIPTION OF THE 8051 4 8051 family members (e.g., 8751, 89C51, 89C52, DS89C4x0) come in different packages, such as DIP (dual in-line package), QFP (quad flat package), and LLC (leadless chip carrier). All have 40 pins that are dedicated to various functions such as I/O, RD, WR, address, data, and interrupts. Some companies provide a 20-pin version of the 8051 with a reduced number of I/O ports for less demanding applications. DIP - dual in-line package 5 QFP - quad flat package 6 LLC - leadless chip carrier 7 SECTION 8.1: PIN DESCRIPTION OF THE 8051 8 Of the 40 pins, 32 pins are for the four ports P0, P1, P2, and P3. The rest of the pins are designated as Vcc, GND, XTAL1, XTAL2, RST, EA, PSEN, and ALE. Vcc, GND, XTAL1, XTAL2, RST, and EA are used by all members of the 8051 and 8031 families and they must be connected in order for the system to work. SECTION 8.1: PIN DESCRIPTION OF THE 8051 9 Vcc - Pin 40 provides supply voltage to the chip. The voltage source is +5V. GND - Pin 20 is the ground. XTALI and XTAL2 The 8051 has an on-chip oscilator but requires an external clock to run it. Most often a quartz crystal oscillator is connected to inputs XTAL1 (pin 19) and XTAL2 (pin 18). XTAL 1 and XTAL2 also needs two capacitors of 30 pF value. XTAL1 and XTAL2 10 XTAL1 and XTAL2 11 RST 12 RST 13 Pin 9 is the RESET pin. It is an input and is active high (normally low). Upon applying a high pulse to this pin, the microcontroller will reset and terminate all activities. This is often referred to as a power-on reset. Figure 8–3b Power-On RESET with Momentary Switch 14 Port 0 15 Also designated as ADO - AD7, allowing it to be used for both address and data. When connecting an 8051/31 to an external memory, port 0 provides both address and data. The 8051 multiplexes address and data through port 0 to save pins. ALE indicates if P0 has address or data. When ALE = 0, it provides data D0 - D7, but when ALE = 1 it has address A0 - A7. Therefore, ALE is used for demuliplexing address and data with the help of a 74LS373 latch. Figure 8–5 Minimum Connection for 89C51/52Based Systems 16 P1 and P2 17 In 8051-based systems with no external memory connection, both P1 and P2 are used as simple I/0. In 8031/51-based systems with external memory connections, port 2 must be used along with P0 to provide the 16-bit address for the external memory. Port 2 is also designated as A8 -A15, indicating its dual function. Since an 8031/51 is capable of accessing 64K bytes of external memory, it needs a path for the 16 bits of the address. While P0 provides the lower 8 bits via A0 - A7, it is the job of P2 to provide bits A8 - A15 of the address. In other words, when the 8031/51 is connected to external memory, P2 is used for the upper 8 bits of the 16-bit address, and it cannot be used for I/0. Port 3 18 Port 3 occupies a total of 8 pins, pins 10 through 17. It can be used as input or output. P3 does not need any pull-up resistors, the same as P 1 and P2 did not. Although port 3 is configured as an input port upon reset, this is not the way it is most commonly used. Port 3 has the additional function of providing some extremely important signals such as interrupts. P3.0 and P3.1 are used for the RxD and TxD serial communications signals. Bits P3.2 and P3.3 are set aside for external interrupts. Bits P3.4 and P3.5 are used for Timers 0 and 1. P3.6 and P3.7 are used to provide the WR and RD signals of external memory connections. Table 8–1Port 3 Alternate Functions 19 Table 8–2 RESET Value of Some 8051 Registers 20 Table 8–3 Clocks per Machine Cycle (MC) for Various 8051 Versions 21 SECTION 8.3: EXPLAINING THE INTEL HEX FILE 22 Intel hex file is a widely used file format designed to standardize the loading of executable machine codes into a ROM chip. Loaders (ELNEC) that come with every ROM burner (programmer) support the Intel hex file format. Program list file for test program 23 The list file for the test program is given in Figure 8-8. The LOC and OBJ fields in Figure 8-8 must be noted. The location is the address where the opcodes (object codes) are placed. The LOC and OBJ information is used to create the hex file. Figure 8-8. List File For Test Program (Assembly) 24 Analyzing Intel hex file 25 Analyzing Intel hex file The ELNEC uses the hex file to download the opcodes into flash memory, The hex file must provide: – – – 26 (1) the number of bytes of information to be loaded, (2) the information itself, and (3) the starting address where the information must be placed. Analyzing Intel hex file Each line of the hex tile consists of six parts. 1. ":" Each line starts with a colon. 2. CC, the count byte. This tells the loader how many bytes are in the line. CC can range from 00 to 16 (10 in hex). 3. AAAA is for the address. This is a 16-bit address. The loader places the first byte of data into this memory address. 4. TT is for type. This field is either 00 or 01. If it is 00, it means that there are more lines to come after this line. If it is 01, it means that this is the last line and the loading should stop after this line. 27 Analyzing Intel hex file 28 5. DD...... D is the real information (data or code). There is a maximum of 16 bytes in this part. The loader places this information into successive memory locations of ROM. 6. SS is a single byte. This last byte is the checksum byte of everything in that line. The checksum byte is used for error checking.The checksum byte at the end of each line represents everything in that line and not just the data portion. 29 30 Next … Lecture Problems Textbook Chapter 8 – Answer as many questions as you can and submit via MeL before the end of the lecture. – Proteus Exercise 8 – 31 Do as much of the Proteus exercise as you can and submit via MeL before the end of the lecture.