Voltage Transfer Characteristic, BJT Biasing 1

advertisement

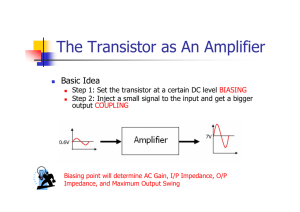

Recall Last Lecture DC Analysis and Load Line Input load line is based on the equation derived from BE loop. Output load line is derived from CE loop. To complete your load line parameters: Obtained the values of IB from the BE loop Get the values of x and y intercepts from the derived IC versus VCE. Draw the curve of IB and obtained the intercept points IC and VCE (for npn) or VEC (for pnp) which is also known as the Q points Voltage Transfer Characteristic VO versus Vi Voltage Transfer Characteristics - npn A plot of the transfer characteristics (output voltage versus input voltage) can also be used to visualize the operation of a circuit or the state of a transistor. Given VBEon = 0.7V, = 120, VCEsat = 0.2V, Develop the voltage transfer curve Vo (V) Cutoff 5 0.7 •In this circuit, Vo = VC = VCE • Initially, the transistor is in cutoff mode because Vi is too small to turn on the diodes. In cut off mode, there is no current flow. • Then as Vi starts to be bigger than VBEon the transistor operates in forward-active mode. Vi (V) Active Mode BE Loop 100IB + VBE – Vi = 0 IB = (Vi – 0.7) / 100 CE Loop ICRC + VO – 5 = 0 IC = (5 – VO) / 4 βIB = (5 – VO) / 4 β = 120 IB = (5 – VO) / 480 Equate the 2 equations: (Vi – 0.7) / 100 = (5 – VO) / 480 Vo = - 480 Vi + 836 A linear equation with negative slope 100 Vo (V) Cutoff 5 Active Saturation 0.2 Vi (V) 0.7 1.7 x 5 To find point x, the coordinate is (x, 0.2) However, as you increase Vi even further, it reaches a point where both diodes start to become forward biased – transistor is now in saturation mode. In saturation mode, VO = VCEsat = 0.2V. So, what is the starting point, x, of the input voltage, Vi when this occurs? Need to substitute in the linear equation Vi = 1.7 V and VO stays constant at 0.2V until Vi = 5V Voltage Transfer Characteristics - pnp Vo (V) saturation Vo = 4.8 VEB VEC β = 80 •Vo = VC and VE = VCC •Hence, VEC = VCC – VO VO = VCC - VEC Vi (V) • As Vi starts from 0V, both diodes are forward biased. Hence, the transistor is in saturation. So, VEC = VECsat and Vo = VCC – VEC sat As Vi increases, VB will become more positive than VC, the junction C-B will become reverse-biased. The transistor goes to active mode. The point (point x) where the transistor start to become active is based on the equation which is derived from active mode operation BE Loop 200IB + 0.7 + Vi – 5 = 0 IB = (4.3 – Vi ) / 200 CE Loop ICRC - VO = 0 IC = VO / 8 80 IB = VO / 8 IB = VO / 640 VEB VEC β = 80 Equate the 2 equations: (4.3 - Vi) / 200 = VO / 640 Vo = - 640 Vi + 2752 200 A linear equation with negative slope Vo (V) saturation Vo = 4.8 VEB VEC β = 80 Active To find point x, the coordinate is (x, 4.8) cutoff 2.8xV 4.3 5 Vi (V) By increasing Vi even more, the potential difference between VEB becomes less than VEBON, causing junction E-B to become reversed biased as well. The diode will be in cut off mode. VO = 0V Using the equation derived: Vo = - 640 Vi + 2752 200 when Vo = 0, then, Vi = 4.3 V Bipolar Transistor Biasing Bipolar Transistor Biasing • Biasing refers to the DC voltages applied to the transistor for it to turn on and operate in the forward active region, so that it can amplify the input AC signal Proper Biasing Effect Ref: Neamen Effect of Improper Biasing on Amplified Signal Waveform Ref: Neamen • Three types of biasing Fixed Bias Biasing Circuit Biasing using Collector to Base Feedback Resistor Voltage Divider Biasing Circuit Biasing Circuits – Fixed Bias Biasing Circuit The circuit is one of the simplest transistor circuits is known as fixed-bias biasing circuit. There is a single dc power supply, and the quiescent base current is established through the resistor RB. The coupling capacitor C1 acts as an open circuit to dc, isolating the signal source from the base current. Typical values of C1 are in the rage of 1 to 10 μF, although the actual value depends on the frequency range of interest. Example – Fixed Bias Biasing Circuit Determine the following: (a) IB and IC (b) VCE (c) VB and VC NOTE: Proposed to use branch current equations and node voltages