Electronics I - Laboratory 5 Rev A Biasing a BJT

advertisement

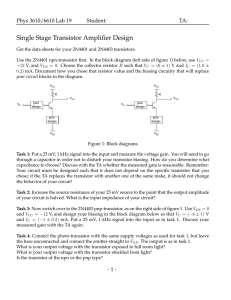

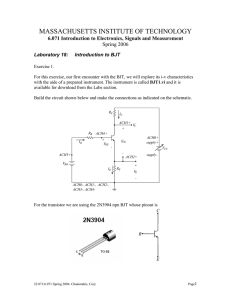

Electronics I - Laboratory 5 Rev A Biasing a BJT I. Objectives 1. Understand the purpose of biasing a transistor. 2. Bias a transistor to a selected quiescent point (Q-point) using the Base Bias and VoltageDivider methods. II. Pre-Lab Requirements 1. Biasing a Transistor In the previous lab, you developed the collector characteristic curves from empirical data. What the chart of this data showed, in essence, was a map of where to operate your particular transistor. There are 3 areas where a transistor can operate; in the saturation region, in the cutoff region, or the active region. a. In the cutoff region, the collector current consists only of leakage current which is extremely low (a few nA) and therefore the voltage drop across the collector-to-emitter (VCE) junction is equal (or very, very nearly equal) to the supply (Vcc) voltage. When operating in the cutoff region the transistor is effectively an open switch. To be in cutoff, both the transistor’s base-toemitter junction and base-to-collector junction must be reversed biased. b. In the saturation region, the voltage drop across the collector-to-emitter junction is very small; therefore, the collector current (IC) flows relatively unimpeded. When operating in saturation, the transistor is effectively a closed switch. To be in saturation, both the transistor’s base-to-emitter junction and base-to-collector junction must be forward biased. c. The active region is the region where the transistor operates as a current amplifier. In this region the collector current (IC) is controlled by the base current (IB) according to the relationship: DC*IB = IC. To be in the active region, the transistor’s base-to-emitter junction must be forward biased and base-to-collector junction must be reversed biased. The term biasing a transistor means setting the transistor’s base current (IB) and collector current (IC) in order to place its operating point at a desired location within the characteristic curve chart. See Figure 1. This “operating point” is referred to as the quiescent point or Q-point because this point should be stationary or “quiescent” while output current (IC) will “operate” (increase and decrease) around this point as a function of the base current (IB). If the Q-point moves around during transistor operation then the output current will not faithfully represent the input current (i.e. the output lacks fidelity). 1 of 8 Figure 1. Location of a Quiescent Point (Q-point) 2. Methodology for Biasing a Transistor Using a Base Biasing Scheme. In the previous lab, where the collector characteristic curves were developed for the 2N3904 transistor, a voltage source was used to control IB and another voltage source was use to control IC. The use of two separate voltage sources complicates design and increases the component count for your circuit. A biasing method employing a single voltage source is more desirable. Figure 2 shows a simple biasing scheme often referred to as base biasing. Figure 2. Base Biasing Scheme for an NPN Transistor 2 of 8 Determine Vcc In the base biasing scheme, the supply voltage (Vcc) is the first parameter to be determined. This is done by picking an appropriate voltage based on an analysis of transistor limitations, circuit limitations, and power supply limitations. Determine Q-Point With the value of Vcc determined, the location of the desired Q-point must now be selected based on input and output considerations. When you are using a transistor as an amplifier, the collector current, which is the output, is controlled by the magnitude of the base current which is the input. Your input will generally be an alternating signal that will have some peak-to-peak value and your goal is to reproduce that input signal at the output with gain and a high degree of fidelity. To do this, the full range of your input and output signals must remain within the active region of the transistor’s operation. Therefore, when designing your amplifier circuit you need to know or approximate what your input current will be. When you have determined this input current range, select its midpoint: This will be your IB bias value. Since IB is represented by a curve on your plots, your next step is to select a single point on that IB curve. This is done by picking a collector-to-emitter voltage value. A general rule is to set VCE equal to half of VCC which places the Q-point near the center of the active region. Where the value of VCE (represented on the Y-axis) and the value of IB cross is your Q-point. With the Q-point selected, your final step is to determine the value of IC at the Q-point. To do this, extend a horizontal line from the Q-point through the Y-axis. Its point of interception with the Y-axis is the value of IC for the selected Q-point. You should now have Q-point bias values for the following parameters: a. IB b. VCE c. IC Determining Values for Rb and Rc Using the relationships for IB, IC, VCE and VBE shown in Figure 2, values for the collector and base resistors can be computed. 3. Methodology for Biasing a Transistor Using a Voltage Divider Biasing Scheme. The base biasing scheme is simple to implement; however, the Q-point can shift if the transistor’s changes from temperature transients or replacement of the transistor itself. Figure 3 shows a different biasing scheme. This biasing scheme called voltage divider biasing helps to mitigate the problems encountered with the base biasing method. The steps below will help you arrive at the component values required to bias your transistor so it operates in the active region at its desired Q-pt. 3 of 8 Figure 3. Voltage Divider Biasing Scheme for an NPN Transistor a. Determining values for VCE and Vcc. Select a value for Vcc. This can be done by considering the voltage sources available for your circuit as well as the maximum collector-emitter voltage (VCEO) from the specification sheet. With Vcc determined set your VCE equal to half Vcc. This will allow you to operate near the center of the active region. VCE = Vcc/2 b. Determining values for IC and IB. With Vcc and VCE set, the next parameter to determine is the collector current, IC. This can be determined by one of two ways: If you know the proposed value of IB then, from the intersection of VCE and the IB curve, extend a horizontal line from that point (the Q-point) through the Y-axis. Its point of interception with the Y-axis is the value of IC for the selected Q-point. If you don’t have a proposed value for IB, select a value for IC that places it in the center of the active region and then extend a horizontal line from this location on the Y-axis of the collector characteristic curves graph until it intersects the vertical line from your selected VCE on the X-axis. At this point in your design you should now have Vcc, VCE, IC and IB determined. 4 of 8 c. Determining values for RC and RE. The next step in your design is to determine the values of the collector resistor (RC) and the emitter resistor (RE). Remember, the emitter current (IE) consists of the collector current (IC) and the base current (IB) in the following relationship: IE = IB + IC and IC = DC * IB and since DC ≈ 100 then IB is small in relation to IC, therefore, IB’s magnitude can, for initial design considerations, be disregarded making the following relationship hold true: IE ≈ IC Looking at Figure 3, it can be seen that: Vcc = (IC * RC) + VCE + (IE * RE) and since IE ≈ IC then: Vcc = (IC * RC) + VCE + (IC * RE) and Vcc = ((IC * (RC + RE)) + VCE so RC + RE = (Vcc - VCE) / IC To determine a value for RE it must be realized that VE should remain relatively stable or fixed as VBE changes. When forward biased, VBE will nominally be about 0.7V (for silicon) but can vary by as much as ±0.15V due to junction temperature changes within the transistor. To account for this undesired change, a value for VE must be set so that the undesired change accounts for less than a 10% change in the value VE. An acceptable value of for VE then would be 1.5V (i.e. 0.15V/1.5V = 0.10). Using 1.5V for VE and the previously selected value of IC, RE can now be determined in accordance with Ohm’s law: VE = IC * RE (since IC≈IE) RE = VE/IC Once RE is determined, RC can easily be found using the following equation: RC = ((Vcc - VCE) / IC) - RE 5 of 8 d. Determining values for R1 and R2. To determine the values for the voltage divider made up of R1 and R2, the base voltage (VB) must be determined. VB is computed using the parameter VBE which is nominally 0.7 V for a forward biased silicon semiconductor junction and the parameter VE which was determined above in step c. VB = VBE + VE With VB known, the final step in your design effort is to determine the values of the resistors, R1 and R2. These resistors are configured as a voltage divider and an acceptable design guideline is to have the current that flows through these resistors be equal to 10 times the base current (IB). Since the collector current was previously set, the value for IB can be determined by the equation: IC = DC* IB And therefore IB = IC / DC Applying the design guideline for the voltage divider current I Voltage Divider = 10* IB Now, knowing the value for IVoltage Divider, the value for the series combination of R1 and R2 can be determined: Knowing the value for VB and applying the voltage divider formula, the values for R1 and R2 can be determined: 6 of 8 4. III. Laboratory Requirements 1. Required Parts and Equipment A. B. C. D. E. F. G. 1 - DC power supplies 1 - Bench DMM 1 - Fluke hand-held DMMs 1 - Proto-Board (PB-103) 1 – 2N3904 Transistor Resistors as required by student’s design Wires and leads for circuit connections. 2. Required Information A. Transistor Data Sheets The following is a link to the specification sheet for the 2N3904: http://www.fairchildsemi.com/ds/2N/2N3904.pdf B. 2N3904 Pinout Figure 4 shows the pin orientation for the 2N3904 Figure 4. 2N3904 Pin Orientation C. 2N3904 collector characteristic curves developed from Lab 4. 3. Laboratory Procedure A. Base Biasing a 2N3904 In this experiment a 2N3904 transistor will be biased using a base biasing scheme in order to place its Q-point at a predicted location within the active region of the characteristic curve chart developed in Lab 4. The transistor parameters will be measured to verify compliance with the designed parameters. a. Design your biasing circuit and develop its schematic in PSpice. b. Construct your designed circuit on a Protoboard. c. Test your circuit and record the parameters in Table 1. 7 of 8 Parameter Measured Value Designed Value Vcc IC VC VE VCE VB IB DC Table 1. Parameter Table for Base Biased 2N3904 B. Voltage Divider Biasing a 2N3904 In this experiment a 2N3904 transistor will be biased using a voltage divider biasing scheme in order to place its Q-point at a predicted location within the active region of the characteristic curve chart developed in Lab 4. The transistor parameters will be measured to verify compliance with the designed parameters. a. Design your biasing circuit and develop its schematic in PSpice. b. Construct your designed circuit on a Protoboard. c. Test your circuit and record the parameters in Table 2. Parameter Vcc IC VC VE VCE VB IB DC Measured Value Designed Value Table 2. Parameter Table for Voltage Divider Biased 2N3904 4. Data Reduction and Lab Report This Lab submittal will be an informal report. Your report should be in Word with graphics pasted in. A. For each 2N3904 biasing scheme circuit, submit the following: a. PSpice schematic of the circuit with all circuit components labeled. b. A PSpice Bias Point analysis of each biasing circuit showing all pertinent biasing parameters. c. A populated parameters table for each biasing circuit. d. An Excel plot of your 2N3904 collector characteristic curves showing the location of your designed Q-point and your measured Q-point. 8 of 8