1 - UBC Computer Science

advertisement

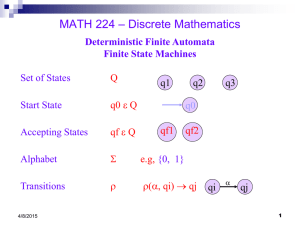

snick snack CPSC 121: Models of Computation 2012 Summer Term 2 Building & Designing Sequential Circuits Steve Wolfman, based on notes by Patrice Belleville and others 1 Outline • Prereqs, Learning Goals, and Quiz Notes • Problems and Discussion – A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs? • Next Lecture Notes 2 Learning Goals: Pre-Class We are mostly departing from the readings to talk about a new kind of circuit on our way to a full computer: sequential circuits. The pre-class goals are to be able to: – Trace the operation of a deterministic finitestate automaton (represented as a diagram) on an input, including indicating whether the DFA accepts or rejects the input. – Deduce the language accepted by a simple DFA after working through multiple example inputs. 3 Learning Goals: In-Class By the end of this unit, you should be able to: – Translate a DFA to a corresponding sequential circuit, but with a “hole” in it for the circuitry describing the DFA’s transitions. – Describe the contents of that “hole” as a combinational circuitry problem (and therefore solve it, just like you do other combinational circuitry problems!). – Explain how and why each part of the resulting circuit works. 4 Where We Are in The Big Stories Theory How do we model computational systems? Now: With our powerful modelling language (pred logic), we can prove things like universality of NOR gates for combinational circuits. Our new model (DFAs) are sort of full computers. Hardware How do we build devices to compute? Now: Learning to build a new kind of circuit with memory that will be the key new feature we need to build fullblown computers! (Something you’ve seen in lab from a new angle.) 5 Outline • Prereqs, Learning Goals, and Quiz Notes • Problems and Discussion – A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs? • Next Lecture Notes 6 Problem: Push-Button Light Switch Problem: Design a circuit to control a light so that the light changes state any time its “push-button” switch is pressed. (Like the light switches in Dempster: Press and release, and the light changes state. Press and release again, and it changes again.) ? 7 A Light Switch “DFA” ? pressed light off light on pressed This Deterministic Finite Automaton (DFA) isn’t really about 8 accepting/rejecting; its current state is the state of the light. Problem: Light Switch ? Problem: Design a circuit to control a light so that the light changes state any time its “push-button” switch is pressed. Identifying inputs/outputs: consider Which are most useful for these possible inputs and outputs: this problem? Input1: the button was pressed Input2: the button is down Output1: the light is on Output2: the light changed states a. b. c. d. e. Input1 and Output1 Input1 and Output2 Input2 and Output1 Input2 and Output2 None of these 9 COMPARE TO: ? Lecture 2’s Light Switch Problem: Design a circuit to control a light so that the light changes state any time its switch is flipped. Identifying inputs/outputs: consider Which are most useful for these possible inputs and outputs: this problem? Input1: the switch flipped Input2: the switch is on Output1: the light is on Output2: the light changed states a. b. c. d. e. Input1 and Output1 Input1 and Output2 Input2 and Output1 Input2 and Output2 None of these 10 Outline • Prereqs, Learning Goals, and !Quiz Notes • Problems and Discussion – A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs? • Next Lecture Notes 11 Departures from Combinational Circuits MEMORY: We need to “remember” the light’s state. EVENTS: We need to act on a button push rather than in response to an input value. 12 Problem: How Do We Remember? We want a circuit that: • Sometimes… remembers its current state. • Other times… loads a new state to remember. Sounds like a choice. 13 What circuit element do we have for modelling choices? Worked Problem: “Muxy Memory” How do we use a mux to store a bit of memory? We choose to remember on a control value of 0 and to load a new state on a 1. ??? 0 output new data 1 control 14 We use “0” and “1” because that’s how MUXes are usually labelled. Worked Problem: Muxy Memory How do we use a mux to store a bit of memory? We choose to remember on a control value of 0 and to load a new state on a 1. old output (Q’) 0 output (Q) new data (D) 1 control (G) 15 This violates our basic combinational constraint: no cycles. Truth Table for “Muxy Memory” Fill in the MM’s truth table: G 0 0 D 0 0 Q' 0 1 a. Q 0 1 b. Q 0 1 c. Q 0 1 d. Q 0 0 0 0 1 1 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 1 1 1 1 0 1 1 1 0 1 1 0 1 0 1 1 X X 1 1 0 1 e. None of these 16 Worked Problem: Truth Table for “Muxy Memory” Worked Problem: Write a truth table for the MM: G D Q' Q 0 0 0 0 0 1 0 1 0 0 1 1 1 1 0 0 0 1 0 1 0 1 0 0 1 1 0 1 1 1 1 1 17 Like a “normal” mux table, but what happens when Q' Q? Worked Problem: Truth Table for “Muxy Memory” Worked Problem: Write a truth table for the MM: G D Q' Q 0 0 0 0 0 1 0 1 0 0 1 1 1 1 0 0 0 1 0 1 0 1 0 0 1 1 0 1 1 1 1 1 18 Q' “takes on” Q’s value at the “next step”. “D Latch” Symbol + Semantics We call a “muxy memory” a “D latch”. When G is 0, the latch maintains its memory. When G is 1, the latch loads a new value from D. old output (Q’) 0 output (Q) new data (D) 1 control (G) 19 D Latch Symbol + Semantics When G is 0, the latch maintains its memory. When G is 1, the latch loads a new value from D. old output (Q’) 0 output (Q) new data (D) 1 control (G) 20 D Latch Symbol + Semantics When G is 0, the latch maintains its memory. When G is 1, the latch loads a new value from D. new data (D) D Q control (G) output (Q) G 21 Hold On!! Why does the D Latch have two inputs and one output when the mux inside has THREE inputs and one output? a. The D Latch is broken as is; it should have three inputs. b. A circuit can always ignore one of its inputs. c. One of the inputs is always true. d. One of the inputs is always false. e. None of these (but the D Latch is not broken as is). 22 Using the D Latch for Circuits with Memory Problem: What goes in the cloud? What do we send into G? D Q ?? G Combinational Circuit to calculate next state input 23 We assume we just want Q as the output. Using the D Latch for Our Light Switch Problem: What do we send into G? D Q ?? current light state G no (0 bit) input a. T if the button is down, F if it’s up. b. T if the button is up, F if it’s down. c. Neither of these. output 24 A Timing Problem: We Need EVENTS! Problem: What do we send into G? D “pulse” when button is pressed button pressed Q current light state G output As long as the button is down, D flows to Q flows through the NOT gate and back to25D... which is bad! A Timing Problem, Metaphor (from MIT 6.004, Fall 2002) What’s wrong with this tollbooth? P.S. Call this a “bar”, not a “gate”, or we’ll tie ourselves in (k)nots. 26 A Timing Solution, Metaphor (from MIT 6.004, Fall 2002) Is this one OK? 27 A Timing Problem Problem: What do we send into G? D “pulse” when button is pressed button pressed Q current light state G output As long as the button is down, D flows to Q flows through the NOT gate and back to28D... which is bad! A Timing Solution (Almost) D D Q G Q G Never raise both “bars” at the same time. button pressed output 29 A Timing Solution D D Q G ?? Q G output The two latches are never enabled at the same time (except for the moment needed for the NOT gate on the left to compute, which is so short that no “cars” get through). 30 A Timing Solution D D Q G button press signal Q G output button pressed 31 Button/Clock is LO (unpressed) 1 1 D 1 LO D Q Q G 0 G 0 output We’re assuming the circuit has been set up and is “running normally”. Right now, the light is off (i.e., the output of the right latch is 0). 32 Button goes HI (is pressed) 1 1 D 1 HI D Q Q G 0 G 1 output This stuff is processing a new signal. 33 Propagating signal.. left NOT, right latch 1 1 D 0 HI D Q Q G 1 G 1 output This stuff is processing a new signal. 34 Propagating signal.. right NOT (steady state) 0 1 D 0 HI D Q Q G 1 G output 1 Why doesn’t the left latch update? a. Its D input is 0. b. Its G input is 0. c. Its Q output is 1. d. It should update! 35 Button goes LO (released) 0 1 D 0 LO D Q Q G 1 G 0 output This stuff is processing a new signal. 36 Propagating signal.. left NOT 0 1 D 1 LO D Q Q G 1 G 0 output This stuff is processing a new signal. 37 Propagating signal.. left latch (steady state) 0 0 D 1 LO D Q Q G 1 G 0 output And, we’re done with one cycle. 38 How does this compare to our initial state? Master/Slave D Flip-Flop Symbol + Semantics When CLK goes from 0 (low) to 1 (high), the flip-flop loads a new value from D. Otherwise, it maintains its current value. new data (D) D D Q control or “clock” signal (CLK) G Q output (Q) G 39 Master/Slave D Flip-Flop Symbol + Semantics When CLK goes from 0 (low) to 1 (high), the flip-flop loads a new value from D. Otherwise, it maintains its current value. new data (D) D D Q control or “clock” signal (CLK) G Q output (Q) G 40 Master/Slave D Flip-Flop Symbol + Semantics When CLK goes from 0 (low) to 1 (high), the flip-flop loads a new value from D. Otherwise, it maintains its current value. new data (D) D D Q control or “clock” signal (CLK) G Q output (Q) G 41 Master/Slave D Flip-Flop Symbol + Semantics When CLK goes from 0 (low) to 1 (high), the flip-flop loads a new value from D. Otherwise, it maintains its current value. Q clock signal new data output D We rearranged the clock and D inputs and the output to match Logisim. 42 Below we use a slightly different looking flip-flop. Why Abstract? Logisim (and real circuits) have lots of flip-flops that all behave very similarly: – – – – D flip-flops, T flip-flops, J-K flip-flops, and S-R flip-flops. They have slightly different implementations… and one could imagine brilliant new designs that are radically different inside. Abstraction allows us to build a good design at a high-level without worrying about the details. Plus… it means you only need to learn about D flip-flops’ guts. 43 The others are similar enough so we can just take the abstraction for granted. Outline • Prereqs, Learning Goals, and !Quiz Notes • Problems and Discussion – A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs? • Next Lecture Notes 44 How Do Computers Execute Programs? • High-level languages (Java/Racket) are translated into low-level machine language • A machine language program is a list of instructions in a representation scheme close to “plain” binary (e.g., 4 bits for the type of instruction, 4 bits for what part of the computer the result goes to, etc.) • Each instruction has a (barely) human-readable version • After it’s done with an instruction, the computer (usually) executes the next instruction in the list 45 Simplified Example (sum of 1..n) (1) (2) (3) (4) (5) (6) (7) sum 0 is n = 0? if the answer was yes, go to (7) sum sum + n nn-1 go to (2) If the computer executed all instructions in order, there’d be no loops or recursion! halt Fortunately, “branch” instructions (like (3)) 46 tell the computer to go elsewhere. Simplified Example, Complicated Execution (1) (2) (3) (4) (5) (6) (7) sum 0 is n = 0? if the answer was yes, go to (7) sum sum + n nn-1 go to (2) To run faster, the computer starts executing one instruction even before it finishes the last. halt But then what does it do with (3)? Does it execute (4) or 47(7)? Branch Prediction Machine To pre-execute a “branch”, the computer guesses which instruction comes next. Here’s one reasonable guess: If the last branch was “taken” (like going to (7) from (3)), take the next. If it was “not taken” (like going to (4) from (3)), don’t take the next. Why? In recursion, how often do we hit 48 the base case vs. the recursive case? Implementing the Branch Predictor (First Pass) Here’s the corresponding DFA. (Instead of accept/reject, we care about the current taken the last branch state.) not taken taken taken yes not taken was taken not taken the last branch was not taken yes we predict the next branch will be taken no we predict the next branch will be not taken no Experiments show it generally works well to add “inertia” 49 so that it takes two “wrong guesses” to change the prediction… Implementing the Branch Predictor (Final Version) Here’s a version that takes two wrong guesses in a row to admit it’s wrong: taken taken YES! not taken yes? taken taken not taken no? not taken NO! not taken Can we build a branch prediction circuit? 50 Abstract Template for a DFA Circuit Each time the clock “ticks” move from one state to the next. clock input store current state compute next state 51 Template for a DFA Circuit Each time the clock “ticks” move from one state to the next. D Q CLK Combinational circuit to calculate next state/output input Each of these lines (except the clock) may carry multiple bits; 52 the D flip-flop may be several flip-flops to store several bits. How to Implement a DFA: Slightly Harder (1) Number the states and figure out b: the number of bits needed to store the state number. (2) Lay out b D flip-flops. Together, their memory is the state as a binary number. (3) Build a combinational circuit that determines the next state given the input and the current state. (4) Use the next state as the new state of the flip-flops. 53 How to Implement a DFA: Slightly Easier MUX Solution (1) Number the states and figure out b: the number of bits needed to store the state number. (2) Lay out b D flip-flops. Together, their memory is the state as a binary number. (3) For each state, build a combinational circuit that determines the next state given the input. (4) Send the next states into a MUX with the current state as the control signal: only the appropriate next state gets used! (5) Use the MUX’s output as the new state of the flipflops. With a separate circuit for each 54 state, they’re often very simple! Implementing the Predictor Step 1 taken taken not taken YES! 3 yes? 2 taken not taken What is b (the number of 1-bit flip-flops needed to represent the state)? a. 0, no memory needed b. 1 c. 2 d. 3 e. None of these taken no? 1 not taken NO! 0 not taken As always, we use numbers to represent the inputs: taken = 1 55 not taken = 0 Just Truth Tables... taken taken Reminder: not taken = 0 taken = 1 YES! 3 take taken no? 1 not taken yes? 2 Current State input New state 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 not taken not taken not taken NO! 0 What’s in this row? a. 0 0 b. 0 1 c. 1 0 d. 1 1 e. None of these. 56 Just Truth Tables... taken taken Reminder: not taken = 0 taken = 1 YES! 3 take taken no? 1 not taken yes? 2 Current State input New state 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 1 1 1 1 not taken not taken not taken NO! 0 57 Implementing the Predictor: Step 3 We always use this pattern. In this case, we need two flip-flops. DD Q Q CLK Combinational circuit to calculate next state/output input 58 Let’s switch to Logisim schematics... Implementing the Predictor: Step 3 DD Q Q CLK ?? sleft input ??? sright 59 Implementing the Predictor: Step 3 sleft ??? sright input 60 Implementing the Predictor: Step 5 (easier than 4!) sleft The MUX “trick” here is much like in the ALU from lab! sright 61 input Implementing the Predictor: Step 4 sleft sright In state number 0, what should be the new value of sleft? Hint: look at the DFA, not at the circuit! a. input b. ~input c. 1 d. 0 62 e. None of these. input Implementing the Predictor: Step 4 sleft sright In state number 1, what’s the new value of sleft? a. input b. ~input c. 1 d. 0 63 e. None of these. input Implementing the Predictor: Step 4 sleft sright In state number 2, what’s the new value of sleft? a. input b. ~input c. 1 d. 0 64 e. None of these. input Implementing the Predictor: Step 4 sleft sright In state number 3, what’s the new value of sleft? a. input b. ~input c. 1 d. 0 65 e. None of these. input Just Truth Tables... sleft sright input sleft' sright' 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 1 1 1 1 66 input Implementing the Predictor: Step 4 sleft sright 67 input Implementing the Predictor: Step 4 In state number 0, what’s the new value of sright? a. input b. ~input c. 1 d. 0 e. None of these. sright 68 input Implementing the Predictor: Step 4 sleft sright TADA!! 69 input You can often simplify, but that’s not the point. sleft sright 70 input Just for Fun: Renaming to Make a Pattern Clearer... taken taken YES! 3 take taken no? 1 not taken yes? 2 pred last input pred' last' 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 1 1 1 1 not taken not taken not taken NO! 0 71 Outline • Prereqs, Learning Goals, and !Quiz Notes • Problems and Discussion – A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs? • Next Lecture Notes 72 Steps to Build a Powerful Machine (1) Number the states and figure out b: the number of bits needed to store the state number. (2) Lay out b D flip-flops. Together, their memory is the state as a binary number. (3) For each state, build a combinational circuit that determines the next state given the input. (4) Send the next states into a MUX with the current state as the control signal: only the appropriate next state gets used! (5) Use the MUX’s output as the new state of the flipflops. With a separate circuit for each 73 state, they’re often very simple! How Powerful Is a DFA? DFAs can model situations with a finite amount of memory, finite set of possible inputs, and particular pattern to update the memory given the inputs. How does a DFA compare to a modern computer? a. Modern computer is more powerful. b. DFA is more powerful. c. They’re the same. 74 Where We’ll Go From Here... We’ll come back to DFAs again later in lecture. In lab you have been and will continue to explore what you can do once you have memory and events. And, before long, how you combine these into a working computer! Also in lab, you’ll work with a widely used representation equivalent to DFAs: regular expressions. 75 Outline • Prereqs, Learning Goals, and !Quiz Notes • Problems and Discussion – A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs? • Next Lecture Notes 76 Learning Goals: In-Class By the end of this unit, you should be able to: – Translate a DFA to a corresponding sequential circuit, but with a “hole” in it for the circuitry describing the DFA’s transitions. – Describe the contents of that “hole” as a combinational circuitry problem (and therefore solve it, just like you do other combinational circuitry problems!). – Explain how and why each part of the resulting circuit works. 77 Next Lecture Learning Goals: Pre-Class By the start of class, you should be able to: – Convert sequences to and from explicit formulas that describe the sequence. – Convert sums to and from summation/”sigma” notation. – Convert products to and from product/”pi” notation. – Manipulate formulas in summation/product notation by adjusting their bounds, merging or splitting summations/products, and factoring out values. 78 Next Lecture Prerequisites See the Mathematical Induction Textbook Sections at the bottom of the “Readings and Equipment” page. Complete the open-book, untimed quiz on Vista that’s due before the next class. 79 snick snack More problems to solve... (on your own or if we have time) 80 Problem: Traffic Light Problem: Design a DFA with outputs to control a set of traffic lights. 81 Problem: Traffic Light Problem: Design a DFA with outputs to control a set of traffic lights. Thought: try allowing an output that sets a timer which in turn causes an input like our “button press” when it goes off. Variants to try: - Pedestrian cross-walks - Turn signals - Inductive sensors to indicate presence of cars - Left-turn signals 82 PROBLEM: Does this accept the empty string? a,b,c b 1 b,c a 2 a 3 c 83 “Moore Machines” DFAs whose state matters A “Moore Machine” is a DFA that’s not about accepting or rejecting but about what state it’s in at a particular time. Let’s work with a specific example... 84