Shillinger_Michael_Presentation,_WLP-TSV_for_IWLPC

advertisement

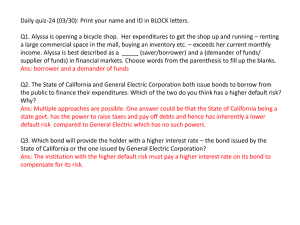

Wafer Level Packaging: A Foundry Perspective Wafer level packaging (WLP) and customized electrical I/O schemes (TSV) have become mature technology platforms. WLP is generally customized to meet specific customer requirements: Die Size Temperature Budget Materials Used Hermiticity Requirements Absolute Pressure Specialized Packaging Wafer Level Packaging Options Low Temperature Metal Alloy Bond High Production Yields (99.1%) – based on 158.000 dies and 592 wafers Low Temperature Bond (160 to 190 C) with High Reflow Temperature (> 500 C) Narrow Bond Line Width (50 to 100 mm) Tightly Controlled Bond Line Thickness (+/- 5 mm) Topography Tolerant (Up to 7000 A) High Bond Strength Histogram of Torque Strength for Metal Alloy WLP 100 Die from 20 Wafers 30 25 Spec 20 Quantity 15 10 5 0 1 2 3 4 5 6 7 8 9 10 11 12 Torque Strength (in-oz) 13 14 15 16 17 18 19 Low Temperature Metal Alloy Bond (Continued) Electrically Conductive Hermetic Compatible across multiple substrates Hermiticity verified on a die by die basis by electrically probing in package thermistors Rh/Rc vs. Pressure After 350 Hours at 110°C Calibration Curve WLP Sealed Die 1.7 1.6 1.5 Rh/Rc 1.4 1.3 1.2 1.1 1 0.1 1 10 Pressure (mT) 100 1000 Low Temperature Metal Alloy Bond (Continued) The reliability of this bond technology was verified a number of time by independent laboratories. 96 hour autoclave at 2 ATM and 121 C SF6 bombing for 1487 hours Air bombing for 1295 hours at 2 ATM Air bombing for 200 hours at 150 C 85 C / 85% RH exposure for 1262 hours Glass Frit Bond Low cost Hermetic High vacuum (<1 mTorr) Bond line widths ~ 400 mm Bond Temperature (400 C) Compatible with getter activation Extremely Strong Withstand 12,000 G acceleration loads Glass Frit Bond (Continued) Topography tolerant Can go over active circuits Providing the correct metallurgy is selected Well characterized reliability Wafer Aligner Wafer Bonder Anodic Bonding Excellent technology for bonding silicon and glass wafers Low temperature (300 C) and low voltage (300 V) is now mature Hermetic Not topography tolerant Bond line widths ~200 mm Bond strength similar to glass frit Excellent reliability characteristics Silicon Fusion Bonding First demonstrated in 1986 and now very mature technology Enables the production of complex structures by combining by combining two or more patterned and etched wafers Bond is extremely strong and hermetic Wafers must be atomically clean and smooth Prior to bond a hydrophilization step is required but this is very predictable Main drawback, high post bond annealing temperatures (~ 1000 C) Prohibits any metals Au / Au Thermo-Compression Bond Hermetic Sputter deposited bond line ~ 50 mm in width Bond temperature ~ 300 C Bond line loading > 5 MPa Not topography tolerant Bond strength not as high as glass frit but higher than eutectic Some commercial bonding systems cannot generate enough clamp force Polymer bonding Not hermetic Effective as a particulate contamination barrier and resistant to fluid penetration Used widely in micro-fluidic circuits Low cost Lithographyically defined bond lines Widths and heights can vary widely to suit various applications Bond temperature low (~ 200 C) WLP Summary All six of the bond technologies reviewed are mature production worthy options Tens of thousands of successful bonds have demonstrated the value of wafer level packaging Sophisticated wafer bonding systems are manufactured by several companies All of the discussed bonds can be performed on these systems Critical component in 3D packaging Allows integration of heterogeneous technologies Reduces packaging cost Allows package size reduction WLP Summary (Continued) When choosing a bond technology various factors need to be considered: Die size and design Available bond line real estate Die topography Device temperature budget Vacuum and hermiticity requirements Die packaging environment Bond line electrical conductivity or dielectric property considerations Electrical I/O Configurations, Through Silicon Vias (TSV) Typical configuration, Solid Copper via with SiO2 insulation through one if the two wafers making up the bonded pair WLP Bond Line Lid Wafer and Device Cavity TSV Back Side Circuits And Bumps Note, the bond line can be patterned to be an electrical circuit Electrical I/O Configurations, Through Silicon Vias (TSV) Typical RF performance data for TSV Single via adds only ~0.01 bB of loss of loss at 6 GHz 0 Via Device #1 Via Device #2 Through Device #1 Through Device #2 -0.01 -0.02 -0.03 Insertion Loss (dB) -0.04 -0.05 -0.06 -0.07 -0.08 -0.09 -0.1 0 1 2 3 Freq (GHz) 4 5 6 Electrical I/O Configurations, Through Silicon Vias (TSV) Historically, the industry has struggled making TSV void free. Recent process advances have overcome this problem 150,000 TSV in a 150 mm wafer with a via yield of 99.9% Electrical I/O Configurations, Through Silicon Vias (TSV) There are specific via design rules that need to be followed 50 x 250um in Reliability testing 50 x 500um demonstrated Electrical I/O Configurations, Through Silicon Vias (TSV) There is virtually no change in via resistance as a function of temperature cycling Electrical I/O Configurations, Through Silicon Vias (TSV) Summary Creation of metal filled vias is a mature high yielding process technology within the MEMS industry TSV technology is the next logical step in providing vertical integration in the semiconductor market driven by space constraints in hand held mobile devices TSV are a major component in 3D packaging Electrical I/O Configurations, Through Silicon Vias (TSV) Summary (Continued) Metal filled vias have the following attributes: Low resistance (0.01 Ohms per via) Low insertion loss for RF applications A vehicle to allow die shrinkage Can vary in diameter from 15 to 50um Can go completely through a 500um wafer Are electrically isolated from the silicon Are compatible with high volume, low cost post wafer chip processing Can be fabricated with a high via yield (99.96%) Conclusion WLP Plus TSV The combination of these two technologies provide significant advantages to MEMS designers in the following areas: Low pressure, low cost packaging Low insertion loss electrical I/Os Low resistance I/Os Smaller chip sizes