Slide_4 - Real-Time Embedded Systems Lab

advertisement

Coldfire Exceptions and Interrupts

Computer Science & Engineering Department

Arizona State University

Tempe, AZ 85287

Dr. Yann-Hang Lee

yhlee@asu.edu

(480) 727-7507

7/23

Building Executable Code

Compile source programs to object code files

Linker to take one or more objects and combines them into a

single executable program

Unix ld, GNU linker

dynamic linker, the part of an OS

main.o

that loads and links the shared

libraries for an executable

symbol resolution

relocation

delay.o

libc.a

linker

executable

library

object

Linker script – to describe how the sections in the input files

should be mapped into the output file, and to control the

memory layout.

7/23

Link Command File (LCF)

Link script in CodeWarrior IDE

Sections in an object file

vector table

text, data, bss, …, ect.

main.text

Memory regions and layout

ROM, RAM, IO space

Location counter

Symbol definition

delay.text

main.data

RAM

main.bss

heap

stack

IO space

7/23

Memory Layout in 5211

32 Kbytes of internal SRAM (215)

256 Kbytes of on-chip flash memory (218)

Memory Base Address Registers (RAMBAR, FLASHBAR) –

base address register sare used to specify the base address of the

internal SRAM and flash modules and indicate the types of references

mapped to each.

Internal Peripheral System Base Address Register (IPSBAR) –

the base address for the 1-Gbyte memory space associated with the onchip peripherals.

Vector Base Register (VBR) –

the base address of the exception vector table in memory

Initial values and RW operations

7/23

Exceptions and Interrupts

The processor is usually in user mode, and enters supervisor

mode when an unexpected event occurs.

There are three different types of exceptions (some are called

interrupts): As a direct result of executing an instruction, such as:

Trap Instruction

Privilege violation

Undefined or illegal instruction

Memory error during fetching an instruction (access error)

As a side- effect of an instruction, such as:

Memory fault during operand read from memory (access error)

Arithmetic error (e. g. divide by zero)

As a result of external hardware signals, such as:

Reset

User peripheral interrupts

set 4 -- 4

Coldfire Exceptions

set 4 -- 5

When an Exception Occurs

Complete the current instruction as best as it can, and

departs from current instruction sequence to handle the

exception by performing the following steps: makes an internal copy of the SR and set SR

S=1 – supervisor mode, T=0 – disable trace, M=0, and I0-I2 = exception

priority (to mask low priority interrupts)

determines the exception vector number.

compute vector if processor exception

performs an interrupt-acknowledge (IACK) bus cycle to obtain the vector

number from the interrupt controller.

saves the “current context” by creating an exception stack frame on

the system stack.

calculates the address of the exception handler (VBR+4*vector

number) and begin to fetch instructions from the handler

set 4 -- 6

Exception Stack Frame

Two longwords are pushed into system stack

PC of the faulting instruction or the next one to be executed

Status register, vector, information on access and address error,

The two longwords are aligned at longword boundary

The original SSP may not be aligned and need a “format field” to calculate the

original SSP

The frame is used for returning from exception (RTE )

RTE – If Supervisor State

Then 2 + (SP) → SR; 4 + (SP) → PC; SP + 8 → SP

Adjust stack according to format field

Synchronizes the pipeline

set 4 -- 7

Reset Exception

Asserting the reset input signal a reset exception

highest priority of any exception

for system initialization and recovery from catastrophic failure.

aborts any processing in progress when the reset input is recognized

Operations

S=1, T=0, M=0, I2-I0=111, VBR=0x00000000

load hardware configuration information into the D0 and D1

Control registers for cache and memory are disabled

loads the first longword at address 0 SSP

load the second longword at address 4 PC and begin the

execution

set 4 -- 8

Exception to Coldfire Core

Peripheral

1

interrupt

IACK

vector

Coldfire core

clear interrupt

Interrupt

controller

Peripheral

2

reset to core

interrupt

configuration

and status

Peripheral

3

Interrupt controller

assign priorities to user interrupts

pending status, masking, forced interrupts

set 4 -- 9

Enable and Disable Interrupts

Set priority level to 0 or 7

void mcf5xxx_irq_enable (void)

{

asm_set_ipl(0);

}

/******************************************/

void mcf5xxx_irq_disable (void)

{

asm_set_ipl(7);

}

asm_set_ipl:

link

A6,#-8

movem.l D6-D7,(SP)

move.w SR,D7

/* current sr

*/

move.l

andi.l

lsr.l

D7,D0

/* prepare return value */

#0x0700,D0 /* mask out IPL */

#8,D0

/* IPL */

move.l

andi.l

lsl.l

8(A6),D6 /* get argument */

#0x07,D6 /* least significant 3bits */

#8,D6 /* move over to make mask */

andi.l

#0x0000F8FF,D7 /* zero out current

IPL*/

or.l

D6,D7

/* place new IPL in sr */

move.w D7,SR

movem.l (SP),D6-D7

lea

8(SP),SP

unlk

A6

rts

set 4 -- 10

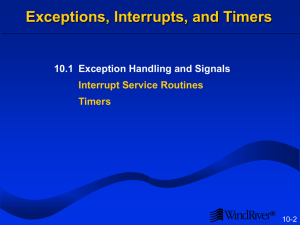

Interrupt Service Routine

function pointer in vector table

void mcf5xxx_set_handler (int vector, void

(*handler) (void))

{

extern uint32 __VECTOR_RAM[];

__interrupt__ void dmaTimer0_handler(void)

{

/* Clear the interrupt from the event register. */

MCF_DTIM0_DTER |=

MCF_DTIM_DTER_CAP |

MCF_DTIM_DTER_REF;

/* interrupt service */

DIRECTION = ~DIRECTION;

__VECTOR_RAM[vector] = (uint32)handler; }

}

mcf5xxx_set_handler(64 + 19,

dmaTimer0_handler);

ISR defined by “interrupt” pragma

the compiler generates a special

prologue and epilogue for the

functions

All modified registers (both

nonvolatileand scratch registers)

are saved or restored,

functions return via RTE instead of

RTS.

set 4 -- 11