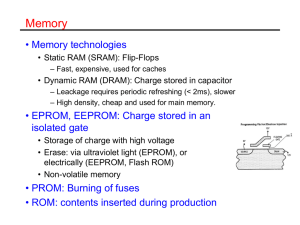

Memory

advertisement

Memory Taken from Digital Design and Computer Architecture by Harris and Harris and Computer Organization and Architecture by Null and Lobur Single-Cycle Processor 31:26 5:0 MemtoReg Control MemWrite Unit Branch ALUControl2:0 Op ALUSrc Funct RegDst PCSrc RegWrite CLK 0 PC' PC 1 A RD Instr Instruction Memory 25:21 20:16 A1 A2 A3 WD3 CLK WE3 RD2 0 SrcB 1 Register File 20:16 + WriteReg4:0 Sign Extend RD Data Memory WD 0 1 <<2 + 15:0 WriteData A ReadData 1 SignImm 4 ALUResult WE 0 15:11 PCPlus4 Zero SrcA RD1 ALU CLK PCBranch Result Copyright © 2007 Elsevier 7-<2> Memory Arrays • Efficiently store large amounts of data • Three common types: – Dynamic random access memory (DRAM) – Static random access memory (SRAM) – Read only memory (ROM) • An M-bit data value can be read or written at each unique Nbit address. Address N Array M Copyright © 2007 Elsevier 5-<3> Data Memory Arrays • Two-dimensional array of bit cells • Each bit cell stores one bit • An array with N address bits and M data bits: – – – – 2N rows and M columns Depth: number of rows (number of words) Width: number of columns (size of word) Array size: depth × width = 2N × M Address Data Address N Array Address 2 3 M Data Data Copyright © 2007 Elsevier Array 5-<4> 11 0 1 0 10 1 0 0 01 1 1 0 00 0 1 1 width depth Memory Array: Example • • • • 22 × 3-bit array Number of words: 4 Word size: 3-bits For example, the 3-bit word stored at address 10 is 100 Example: Address Data Address 2 Array 3 Data Copyright © 2007 Elsevier 11 0 1 0 10 1 0 0 01 1 1 0 00 0 1 1 width 5-<5> depth Memory Arrays Address 10 1024-word x 32-bit Array 32 Data Copyright © 2007 Elsevier 5-<6> Memory Array Bit Cells bitline wordline stored bit Example: bitline = wordline = 1 bitline = wordline = 0 stored bit = 0 stored bit = 0 bitline = wordline = 1 bitline = wordline = 0 stored bit = 1 stored bit = 1 (a) Copyright © 2007 Elsevier (b) 5-<7> Memory Array Bit Cells bitline wordline stored bit Example: bitline = Z bitline = 0 wordline = 1 wordline = 0 stored bit = 0 stored bit = 0 bitline = Z bitline = 1 wordline = 1 wordline = 0 stored bit = 1 stored bit = 1 (a) Copyright © 2007 Elsevier (b) 5-<8> Memory Array • Wordline: – similar to an enable – allows a single row in the memory array to be read or written – corresponds to a unique address – only one wordline is HIGH at any given time 2:4 Decoder 11 Address wordline3 2 10 01 00 Copyright © 2007 Elsevier bitline2 wordline2 wordline1 wordline0 bitline1 stored bit = 0 stored bit = 1 stored bit = 0 stored bit = 1 stored bit = 0 stored bit = 0 stored bit = 1 stored bit = 1 stored bit = 0 stored bit = 0 stored bit = 1 stored bit = 1 5-<9> Data2 Data1 bitline0 Data0 Types of Memory • Random access memory (RAM): volatile • Read only memory (ROM): nonvolatile Copyright © 2007 Elsevier 5-<10> RAM: Random Access Memory • Volatile: loses its data when the power is turned off • Read and written quickly • Main memory in your computer is RAM (DRAM) Historically called random access memory because any data word can be accessed as easily as any other (in contrast to sequential access memories such as a tape recorder) Copyright © 2007 Elsevier 5-<11> ROM: Read Only Memory • Nonvolatile: retains data when power is turned off • Read quickly, but writing is impossible or slow • Flash memory in cameras, thumb drives, and digital cameras are all ROMs Historically called read only memory because ROMs were written at manufacturing time or by burning fuses. Once ROM was configured, it could not be written again. This is no longer the case for Flash memory and other types of ROMs. Copyright © 2007 Elsevier 5-<12> Types of RAM • Two main types of RAM: – Dynamic random access memory (DRAM) – Static random access memory (SRAM) • Differ in how they store data: – DRAM uses a capacitor – SRAM uses cross-coupled inverters Copyright © 2007 Elsevier 5-<13> Robert Dennard, 1932 • • • Invented DRAM in 1966 at IBM Others were skeptical that the idea would work By the mid-1970’s DRAM was in virtually all computers Copyright © 2007 Elsevier 5-<14> DRAM • Data bits stored on a capacitor • Called dynamic because the value needs to be refreshed (rewritten) periodically and after being read: – Charge leakage from the capacitor degrades the value – Reading destroys the stored value bitline bitline wordline wordline stored bit Copyright © 2007 Elsevier stored bit 5-<15> DRAM bitline bitline wordline wordline stored + + bit = 1 Copyright © 2007 Elsevier stored bit = 0 5-<16> SRAM bitline wordline stored bit bitline bitline wordline Copyright © 2007 Elsevier 5-<17> Memory Arrays 2:4 Decoder 11 Address wordline3 2 10 01 00 bitline2 wordline2 wordline1 wordline0 bitline1 stored bit = 0 stored bit = 1 stored bit = 0 stored bit = 1 stored bit = 0 stored bit = 0 stored bit = 1 stored bit = 1 stored bit = 0 stored bit = 0 stored bit = 1 stored bit = 1 Data2 Data1 bitline0 Data0 SRAM bit cell: DRAM bit cell: bitline wordline Copyright © 2007 Elsevier bitline bitline wordline 5-<18> ROMs: Dot Notation bitline wordline 2:4 Decoder 11 Address bit cell containing 0 2 10 bitline wordline 01 bit cell containing 1 00 Data2 Data1 Data0 To read the cell the bitline is weakly pulled high. Copyright © 2007 Elsevier 5-<19> ROM Storage 2:4 Decoder 11 Address Address Data 11 0 1 0 10 1 0 0 01 01 1 1 0 00 00 0 1 1 2 10 Data2 Data1 Data0 Copyright © 2007 Elsevier 5-<20> width depth ROM Logic 2:4 Decoder 11 Address Data2 = A1 A0 Data1 = A1 + A0 2 10 Data0 = A1A0 01 00 Data2 Data1 Data0 Copyright © 2007 Elsevier 5-<21> Example: Logic with ROMs • Implement the following logic functions using a 22 × 3-bit ROM: – X = AB – Y=A+B – Z=AB 2:4 Decoder 11 Address A, B 2 10 01 00 Data2 Data1 Data0 X Copyright © 2007 Elsevier 5-<22> Y z Example: Logic with ROMs • Implement the following logic functions using a 22 × 3-bit ROM: – X = AB – Y=A+B – Z=AB 2:4 Decoder 11 A, B 2 10 01 00 X Copyright © 2007 Elsevier 5-<23> Y Z Logic with Memory Arrays • Called lookup tables (LUTs): look up output at each input combination (address) 4-word x 1-bit Array 2:4 Decoder 00 Truth Table A 0 0 1 1 B 0 1 0 1 Y 0 0 0 1 A A1 B A0 bitline stored bit = 0 01 stored bit = 0 10 stored bit = 0 11 stored bit = 1 Y Copyright © 2007 Elsevier 5-<24> Fujio Masuoka, 1944• Developed memories and high speed circuits at Toshiba from 19711994. • Invented Flash memory as an unauthorized project pursued during nights and weekends in the late 1970’s. • The process of erasing the memory reminded him of the flash of a camera • Toshiba slow to commercialize the idea; Intel was first to market in 1988 • Flash has grown into a $25 billion per year market. Copyright © 2007 Elsevier 5-<25> Reprogrammable ROM Electronically erasable PROM (EEPROM) Flash memory is similar Programmable ROM (PROM) Multi-ported Memories • Port: address/data pair • 3-ported memory – 2 read ports (A1/RD1, A2/RD2) – 1 write port (A3/WD3, WE3 enables writing) • Small multi-ported memories are called register files CLK N N N M Copyright © 2007 Elsevier A1 WE3 A2 A3 RD1 RD2 Array WD3 5-<27> M M Verilog Memory Arrays // 256 x 3 memory module with one read/write port module mem( input clk, we, input [7:0] a input [2:0] wd, output [2:0] rd); reg [2:0] RAM[255:0]; assign rd = RAM[a]; always @(posedge clk) if (we) RAM[a] <= wd; endmodule Copyright © 2007 Elsevier 5-<28> Initializing Memory module mem(input clk, we, input [7:0] a input [2:0] wd, output [2:0] rd); reg [2:0] RAM[255:0]; assign rd = RAM[a]; always @(posedge clk) if (we) RAM[a] <= wd; initial begin $readmemb("memVectors.txt", RAM); end endmodule Parameterized memory module module ram # (parameter N = 6, M = 32) ( input clk, we, input [N-1:0] adr, input [M-1:0] din, output [M-1:0] dout); reg [M-1:0] mem[2**N-1:0]; always @(posedge clk) if (we) mem[adr] <= din; assign dout = mem[adr]; endmodule Copyright © 2007 Elsevier module bigRam (input clk, we, input [9:0] adr, input [31:0] din, output [31:0] dout); // instantiate the ram ram #(10,32) memory(clk, we, adr, din, dout); endmodule 5-<30> Memory Organization • Memory can be byte-addressable, or wordaddressable, where a word typically consists of two or more bytes. • Memory is constructed of RAM chips, often referred to in terms of length width. 31 4.6 Memory Organization • Physical memory usually consists of more than one RAM chip. • Access is more efficient when memory is organized into banks of chips with the addresses interleaved across the chips • With low-order interleaving, the low order bits of the address specify which memory bank contains the address of interest. • Accordingly, in high-order interleaving, the high order address bits specify the memory bank. The next slide illustrates these two ideas. 32 4.6 Memory Organization Low-Order Interleaving High-Order Interleaving 33 4.6 Memory Organization • Example: Suppose we have a memory consisting of 16 2K x 8 bit chips. – – – Memory is 32K = 25 210 = 215 15 bits are needed for each address. We need 4 bits to select the chip, and 11 bits for the offset into the chip that selects the byte. 34 4.6 Memory Organization • In high-order interleaving the high-order 4 bits select the chip. • In low-order interleaving the low-order 4 bits select the chip. 35