FSMs and Verilog

advertisement

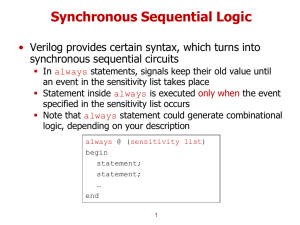

Sequential Logic in Verilog Taken From Digital Design and Computer Architecture David Money Harris and Sarah L. Harris Copyright © 2007 Elsevier 4-<1> Sequential Logic • Verilog uses certain idioms to describe latches, flip-flops and FSMs • Other coding styles may simulate correctly but produce incorrect hardware Copyright © 2007 Elsevier 4-<2> Always Statement General Structure: always @ (sensitivity list) statement; Whenever the event in the sensitivity list occurs, the statement is executed Copyright © 2007 Elsevier 4-<3> D Flip-Flop module flop(input clk, input [3:0] d, output reg [3:0] q); always @ (posedge clk) q <= d; // pronounced “q gets d” endmodule Any signal assigned in an always statement must be declared reg. In this case q is declared as reg Beware: A variable declared reg is not necessarily a registered output. We will show examples of this later. Copyright © 2007 Elsevier 4-<4> Resettable D Flip-Flop module flopr(input clk, input reset, input [3:0] d, output reg [3:0] q); // synchronous reset always @ (posedge clk) if (reset) q <= 4'b0; else q <= d; endmodule clk d[3:0] reset [3:0] [3:0] D[3:0] R Q[3:0] [3:0] [3:0] q[3:0] q[3:0] Copyright © 2007 Elsevier 4-<5> Resettable D Flip-Flop module flopr(input clk, input reset, input [3:0] d, output reg [3:0] q); // asynchronous reset always @ (posedge clk, posedge reset) if (reset) q <= 4'b0; else q <= d; endmodule clk d[3:0] [3:0] [3:0] D[3:0] Q[3:0] [3:0] [3:0] q[3:0] R reset Copyright © 2007 Elsevier q[3:0] 4-<6> D Flip-Flop with Enable module flopren(input clk, input reset, input en, input [3:0] d, output reg [3:0] q); // asynchronous reset and enable always @ (posedge clk, posedge reset) if (reset) q <= 4'b0; else if (en) q <= d; endmodule Copyright © 2007 Elsevier 4-<7> Latch module latch(input clk, input [3:0] d, output reg [3:0] q); always @ (clk, d) if (clk) q <= d; endmodule d[3:0] clk [3:0] [3:0] lat D[3:0] C Q[3:0] [3:0] [3:0] q[3:0] q[3:0] Warning: We won’t use latches in this course, but you might write code that inadvertently implies a latch. So if your synthesized hardware has latches in it, this indicates an error. Copyright © 2007 Elsevier 4-<8> Finite State Machines (FSMs) • Three blocks: – next state logic – state register – output logic inputs Copyright © 2007 Elsevier M next state logic CLK next k state k state output logic N outputs 4-<9> FSM Example: Divide by 3 S2 S0 S1 The double circle indicates the reset state Copyright © 2007 Elsevier 4-<10> FSM in Verilog: Divide by 3 module divideby3FSM (input clk, input reset, output q); reg [1:0] state, nextstate; parameter S0 = 2'b00; parameter S1 = 2'b01; parameter S2 = 2'b10; Copyright © 2007 Elsevier // state register always @ (posedge clk, posedge reset) if (reset) state <= S0; else state <= nextstate; // next state logic always @ (*) case (state) S0: nextstate = S1; S1: nextstate = S2; S2: nextstate = S0; default: nextstate = S0; endcase // output logic assign q = (state == S0); endmodule 4-<11> Moore vs. Mealy FSM • Alyssa P. Hacker has a snail that crawls down a paper tape with 1’s and 0’s on it. The snail smiles whenever the last four digits it has crawled over are 1101. Design Moore and Mealy FSMs of the snail’s brain. Moore FSM reset 1 S0 0 Copyright © 2007 Elsevier 0 S1 0 0 0 1 1 1 S2 0 1 S3 0 0 S4 1 0 Snail Moore Machine • snailMoore.v Copyright © 2007 Elsevier 4-<13> JK Moore Machine Example • 110 Detector designed with JK flip-flops – Design a machine with input A and output Y – Y should be one whenever the sequence 1 1 0 has been detected on A on the last 3 consecutive rising clock edges or ticks. – Otherwise Y = 0 • Timing diagram interpretation of word description Copyright © 2007 Elsevier 4-<14> State Diagram S Copyright © 2007 Elsevier A NS Y 00 (S0) 0 00 (S0) 0 00 (S0) 1 01 (S1) 0 01 (S1) 0 00 (S0) 0 01 (S1) 1 10 (S2) 0 10 (S2) 0 11 (S3) 0 10 (S2) 1 10 (S2) 0 11 (S3) 0 00 (S0) 1 11 (S3) 1 01 (S1) 1 4-<15> Transition Tables J K Q+ 0 0 Q 0 1 0 1 0 1 1 1 ~Q S1 S0 A S1+S0+ J1 K1 J0 K0 Y 0 0 (S0) 0 0 0 (S0) 0 x 0 x 0 0 0 (S0) 1 0 1 (S1) 0 x 1 x 0 0 1 (S1) 0 0 0 (S0) 0 x x 1 0 0 1 (S1) 1 1 0 (S2) 1 x x 1 0 Transition J K 1 0 (S2) 0 1 1 (S3) x 0 1 x 0 0 => 0 0 x 1 0 (S2) 1 1 0 (S2) x 0 0 x 0 0 => 1 1 x 1 1 (S3) 0 0 0 (S0) x 1 x 1 1 1 => 0 x 1 1 1 (S3) 1 0 1 (S1) x 1 x 0 1 1 => 1 x 0 Copyright © 2007 Elsevier 4-<16> Verilog Verilog Implementation 1 Copyright © 2007 Elsevier 4-<17> Verilog 2 Verilog Implementation 2 – JK FlipFlop in Verilog – testBench in Verilog Copyright © 2007 Elsevier 4-<18>