MIP-based Detailed Placer for Mixed-size Circuits

advertisement

MIP-based Detailed

Placer for Mixed-size

Circuits

Shuai Li, Cheng-Kok Koh

ECE, Purdue University

{li263, chengkok}@purdue.edu

Outline

Motivation

Incomplete SCP model

Experimental results

Summary

Background

Placement

Global placement

minimize total wirelength,

estimated with half parameter

wirelength (HPWL)

routability-driven placement

avoid routing congestion

optimized approximate

locations;

Detailed placement

after legalization;

rearrange cells to reduce

HPWL

Detailed placement

cell swap/move technique

FastPlace-DP, global and vertical cell swap/move

congestion-aware FastPlace-DP, routability-driven placers

sliding window technique

partition the whole chip into overlapping windows

moving cells locally in windows has less perturbance to routability

enumeration approach;

solution space O(n!) for n-cell window;

windows with no more than 6 cells

alternative approaches to optimize larger windows

branch-and-bound technique, cell matching technique, etc.

MIP approach for detailed placement

Mixed Integer Programming (MIP) approach

placement of each window is formulated into an MIP problem:

linear objective function & linear constraints;

integer variables

mature mathematical techniques for solving MIP problems

a branch-and-bound tree is built during solution, whose size is

dependent on the number of integer variables

MIP models for detailed placement

the S model, the RQ model, the SCP model

the single-cell-placement (SCP) model

over 10 times more efficient than the other MIP models

MIP-based detailed placer

Parallelized MIP-based detailed placer

IBM Version 2 benchmark circuits

Initial placement results generated with enumeration approach;

1.684% further reduction in HPWL;

0.827% and 1.707% further reduction in routed wirelength and via

count, respectively.

Apply it to recent mixed-size circuits?

benchmark circuits in ISPD11, DAC12, ICCAD12 routability-driven

contests

Challenges with recent mixed-size circuits

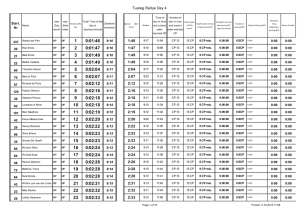

DAC12 benchmark circuits

n.c. number of cells

o.r. occupation rate, the rate that sites are occupied by cells

400 extracted 10-cell windows

n.s. average number of sites

n.v. average number of integer variables in SCP model;

IBM Version 2

DAC12

Our contribution

DAC12 benchmark circuits

over 10 times more cells

over 2 times more sites in sliding windows

over 10 times increase in solution time of each window

Incomplete SCP model

ignore a portion of integer variables in SCP model

great reduction in solution time without much degradation in

solution quality

MIP-based detailed placer for DAC12 benchmark circuits

Outline

Motivation

Incomplete SCP model

Experimental results

Summary

Problem description

Objective: minimize HPWL

Constraints:

1.

2.

no cell overlap;

each cell is placed legally, i.e. cell c occupies exactly wc consecutive

sites in one row

R: set of rows

Q: set of columns

C: set of cells

wc: width of cell c

N: set of nets

Single-cell-placement variables

Single-cell-placement patterns and corresponding vectors

ck single-cell-placement (SCP) variable:

whether the kth pattern to place single cell c is chosen or not

e.g. cell 1 in the 3X7 window;

|R|(|Q|-wc+1)=18 variables in all

SCP Model

definition of bounding box

site occupation

cell centroid and site occupation variables

derived from SCP variables

one pattern for each cell

(llxn, llyn , urxn, uryn): bounding box of net n ;

(xc, yc): centroid of cell c;

pcrq : whether cell c occupies the site at row r and column q

Incomplete SCP Model

definition of bounding box

site occupation

cell centroid and site occupation variables

derived from SCP variables

one pattern for each cell

skipping patterns

Incomplete SCP Model (cont’d)

e.g. cell 1 in the 3X7 window;

|R|(|Q|-wc+1)=18 variables in all

oc = 1, when skip=3, only the 1st, 4th, 7th, 10th, 13th, 16th are kept

Incomplete SCP Model (cont’d)

Guideline to set skip

exact locations in the solution may be non-optimal

guarantee different orders of placing cells are still in the solution

space

skip=1 for compact windows;

larger skip for sparse windows with low occupation rate (ocp_rt)

and more empty sites

Two incomplete SCP models

Number of variables for cell c in SCP model:

vc | R | (| Q | wc 1) c | R || Q |, c (| Q | wc 1)/ | Q |

SCP_OR model, set skip based on occupation rate

skip round(1/ ocp _ rt ) round(| R || Q | / wc )

vc c | R || Q | / skip cO( wc )

c

c

vc is close to summation of cell width, the same as in the SCP model of

placing the same cells in a compact window

SCP_ES model, set skip based on number of empty sites

skip floor(empty_sites_cnt/|C|)+1=floor((1 opt _ rt ) | R || Q | / | C |) 1

vc c | R || Q | / skip

c

|C |

1 ocp _ rt

In compact windows, skip=1

In sparse windows with ocp_rt close to 0.0, vc is close to |C|, the same as in

the SCP model of placing the same number of uniform-width cells

Outline

Motivation

Incomplete SCP model

Experimental results

Summary

Effect of incomplete models

tolerance time 40s, 60s, 800s for 8-cell, 10-cell, 12-cell windows

SCP_OR model, a good compromise of the SCP model

fewer than a half integer variables (n.v. )

over 6 times faster (t(s)), within 10% degradation in HPWL reduction (red.)

SCP_ES model

1/5 variables, 100 times faster with 40% degradation

used in our parallelized MIP-based detailed placer

Enumeration approach (ENUM)

few windows are optimized with the same tolerance time

Results on DAC12 benchmark circuits

MIP-based detailed placer

2-row and 4-row windows with no more than 10 cells

windows are scanned for 3 times

Initial placement results generated by different placers

Ripple

NTUPlace4

Two commercial routers to generate detailed routing solutions

Router A, Router B

existing translator from Bookshelf files to LEF/DEF files

W.-H. Liu et al. Case study for placement solutions in ISPD11 and DAC12 routability-driven

placement contests. In Proc. ISPD, pages 114–119, 2013.

Effects on Ripple’s results

INIT: initial results generated with congestion-aware FastPlace-DP

MIP: results after MIP-based detailed placer

Router A

WL(e7): routed wirelength

VIA(e7): via count

VIO: number of detailed routing violations T(m): routing run-time

OF: overflows in global routing

Effects on NTUPlace4’s results

INIT: initial results generated with cell matching technique

MIP: results after MIP-based detailed placer

Router A

WL(e7): routed wirelength

VIA(e7): via count

VIO: number of detailed routing violations T(m): routing run-time

OF: overflows in global routing

Effects on Ripple’s results

INIT: initial results generated with congestion-aware FastPlace-DP

MIP: results after MIP-based detailed placer

Router B

Effects on NTUPlace4’s results

INIT: initial results generated with cell matching technique

MIP: results after MIP-based detailed placer

Router B

Outline

Motivation

Incomplete SCP model

Experimental results

Summary

Summary

MIP approach for detailed placement

optimize larger sliding windows to further reduce wirelength

Application in recent large-scale benchmark circuits

Over 10 times more cells;

Lower occupation rate leading to significant increase in the solution

time of each window

Incomplete SCP model

ignore variables to significantly decrease solution time;

Despite degradation in solution quality, still effective reduction in

wirelength is achieved without perturbance of routability

Thank you!

Large-scale mixed-size circuits

Larger solution space for windows with more empty sites

1-row window with n cells and m empty sites

More integer variables in MIP results in the increase of solution time

Over 300 randomly extracted windows

#cell

t(s)

opt

for each size

ibm01: IBM Version 2 benchmark

tolerance time 40s

ibm01

s16: DAC12 benchmark

tolerance time 40s, 60s, 800s for 8-cell,

10-cell, 12-cell windows, respectively

longer average solution time t(s)

s16

lower optimization rate opt

8-cell

0.82

100%

10-cell

1.93

99.7%

12-cell

5.86

96.4%

8-cell

9.2

94.4%

10-cell

19.6

90.7%

12-cell

113.3

76.8%