Part two

advertisement

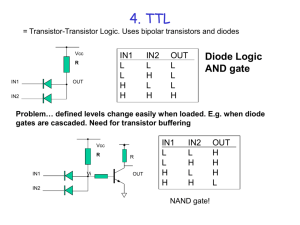

Topic 4: Digital Circuits (Integrated Circuits Technology) Part two Logic Levels: Practical Scenario • The two sets of levels are motivated by these scenarios Valid input VOHMIN Valid output VIHMIN RTH Rline Vcc RIN Vdrop Scenario 1: Source outputs logic high at lowest threshold, VOHMIN I SINK SOURCE Valid input Vcc VOLMAX Valid output VILMAX RTHL Rline RIN I SINK SOURCE Scenario 2: Source outputs logic low at highest threshold, VOLMAX DC Loading • The output high and low limits are exceeded only if a device output is heavily loaded. Logic device loading is specified by – maximum current – Fanout := max. number of similar devices that can be connected to a load without exceeding high and low state current limits Current Specs IOHMAX Max source current for which VOH VOHMIN (valid output high) IOLMAX Max sink current for which VOL VOLMAX (valid output low) IIHMAX Max input current for VIH VIHMIN (valid input high) IILMAX Max input current for which VIL VILMAX (valid input low) DC Loading: Current specs Valid input IIHMAX1 1 Vo > VOHMIN Io < IOHMAX n IIHMAXn Valid input IILMAX1 Vo < VOLMAX 1 Io < IOLMAX IILMAXn • Scenario 1: Output high connected to more than one sink. The current outputted by the source increases with the number of sinks. Io = Iinj = nIin (for n similar sinks) n • Scenario 2: Output low connected to more than one sink. Note that the current now flows into the output terminal (logic source becomes a current sink). Again current increases with the number of logic sinks. Io = Iinj = nIin (for n similar sinks) DC Loading: Fanout • Each gate input requires a certain amount of current to maintain it in the LOW state or in the HIGH state. – IIL and IIH – These are specified by the manufacturer. I OL maxdriver nFlow I ILdriven nFhigh I OH maxdriver I IH driven Fanout calculation –Low state fanout, nFlow:= maximum number of similar gates that can be driven low so that Vo < VOLMAX –High state fanout, nFhigh:= maximum number of similar gates that can be driven high so that Vo > VOHMIN –Need to do current loading calculation for non-gate loads (LEDs, termination resistors, etc.) Fanout, nF minnFlow, nFhigh AC Loading • • All gate outputs have associated parasitic capacitances due to external wiring (including their gate pins) as well as internal semiconductor storage effects (junction capacitances). In addition there are parasitic capacitances associated with each gate input. Typically the capacitance component due to IC pins is of the order of 10-15pF. The final transistor which drives the gate output acts as an electronically controlled switch with a pull-up to Vcc. Vcc R Vo Parasitic capacitance, Cp Contact resistance, r Switch closed: Vo = 0 Switch opens: Cp charges to Vcc with LH=RCp. Switch closes: Cp discharges through contact resistance, r, with HL=rCp. 3. CMOS Technology • Static complementary CMOS - except during switching, output connected to either VDD or GND via a low-resistance path – high noise margins • full rail to rail swing • VOH and VOL are at VDD and GND, respectively – low output impedance, high input impedance – no steady state path between VDD and GND (no static power consumption) – delay a function of load capacitance and transistor resistance – comparable rise and fall times (under the appropriate transistor sizing conditions) • Dynamic CMOS - relies on temporary storage of signal values on the capacitance of high-impedance circuit nodes – simpler, faster gates – increased sensitivity to noise 3.1. CMOS Circuit Topology Pull-up network (PUN) and pull-down network (PDN) VDD PMOS transistors only In1 In2 PUN InN In1 In2 InN pull-up: make a connection from VDD to F when F(In1,In2,…InN) = 1 F(In1,In2,…InN) PDN pull-down: make a connection from F to GND when F(In1,In2,…InN) = 0 NMOS transistors only PUN and PDN are dual logic networks b) Dual PUN and PDN • PUN and PDN are dual networks – DeMorgan’s theorems • (A + B)’ = A’.B’ • (A.B)’ = A’ + B’ – a parallel connection of transistors in the PUN corresponds to a series connection of the PDN • Complementary gate is naturally inverting (NAND, NOR, NOT) • Number of transistors for an N-input logic gate is 2N CMOS Complements PDN PUN 3.2 Examples of CMOS Gates VDD = 5V Vi 0(L) 5(H) Q2 p-channel Vo Vi Q1 n-channel CMOS inverter Q1 OFF ON Q2 Vo ON 5(H) OFF 0(L) CMOS NAND • Use 2n transistors for n-input gate • p-channel in parallel, n-channel in series • Add output inverter to convert to AND CMOS NOR • Like NAND -- 2n transistors for n-input gate • p-channel series, n-channels in parallel NAND vs NOR • For a given silicon area, PMOS transistors are have higher ON resistance than NMOS transistors => Output High voltage is lower due to series connection in NOR. NOR NAND •NAND output LOW voltage is not as badly compromised • Result: NAND gates are preferred in CMOS. CMOS characteristics • Essentially no DC current flow into MOS gate terminal • Gate has capacitance, C which MUST be charged then discharged for switching • Required power is CPDV2f ; where f is switching frequency, CPD is the power dissipation capacitance • Very little (0(nA)) current in output chain, except during switching when both transistors are partially on • More power required when signal rise times are small since transistors are on longer • Symmetric output structure ==> equally strong drive (IOH, IOL) in LOW and HIGH states This is why.. 1. Power dissipation in PCs increase with clock frequency 2. There is a lot of research on low voltage logic devices (5V, now 3.3V common) CMOS families and typical specifications • VOHMIN=VDD-0.1V, VIHMIN=0.7Vcc, VILMAX=0.3VDD, VOLMAX=0.1V • 3V VDD 18V (original 4000 family), 2V VDD 6V (newer HC family) • Input source and leakage currents: <1A • Output current: typically 4mA but can be as high as 24mA • Families: original 4000 family (slower, lower power dissip.) – 74FAMnnn: FAM = family type, nnn=function number – faster – 54FAMnnn: same as 74FAMnnn but for military apps. – FAM : HC (High Speed CMOS), HCT (HC TTL compatible), VHC/VHCT (Very High speed), FCT/FCT-T(Fast CMOS TTL compatible/ with TTL VOH) – Egs: 74HC04 – hex inverter. IOLMAX=20 A, IOHMAX=-20A. • NB: Special handling precautions hold as CMOS can be damaged by very a small electrostatic discharge 4. TTL = Transistor-Transistor Logic. Uses bipolar transistors and diodes Vcc IN1 L L H H R IN1 OUT IN2 IN2 L H L H OUT L L L H Diode Logic AND gate Problem… defined levels change easily when loaded. E.g. when diode gates are cascaded. Need for transistor buffering Vcc R IN1 IN2 Vi R OUT IN1 L L H H IN2 L H L H NAND gate! OUT H H H L TTL: practical realisation Diode AND gate Dynamic resistance: lower ON (L) voltage, faster switching Limits current in transition Totem Pole Output Schottky Diodes Clamp diodes TTL Logic families and specs • • • • • • • Vcc=5V±10%, Vohmin=2.7V, Vihmin=2.0V, Volmax=0.5V, Vilmax=0.8V NMh = 0.7V, NML=0.3V Families: TTL e.g. 7404, 74H04, 74L04 original family – Schottky e.g. 74S04: faster, hi power consumption – Low Power Schottky e.g. 74LS04: lower Pd, Slower Schottky (common) – Advanced Schottky e.g. 74AS04 2x speed of S, same Pd – Adv. Low Pwr Sky e.g. 74ALS04 see table 3-11, Wakerly For LS, typically: IILmax=-0.4mA, IIHmax=20uA, IOLmax=8mA, IOHmax=-400uA. FANOUT (LSTTL into LSTTL)=20 NB: TTL outputs can sink more current than they can source. TTL vs CMOS TTL CMOS Noise Margins 0.3(high), 0.5 (low) 0.3Vcc Input source currents High in both states: 0.2 to 2mA(L), 20-50uA (H) Typ < 1uA in both states Power Consumption Relatively high, fixed. 2mW for 74LS, 20mW for 74Sxx. Depends on Vcc, frequency. Negligible static dissipation. Very low for FCTT Output drive current Asymmetric: High state: 0.4-2mA Low state: 8 – 20mA Symmetric: Typ 4mA but AC family can drive 24mA Power supply voltage 5V ±10% 3V Vcc 18V (original 4000 family), 2V Vcc 6V (newer HC family) Interconnectio n (CMOS to TTL, TTL to CMOS) Cannot drive CMOS since VOHMIN(TTL)<VIHMIN(CMOS) Pullup resistor needed unless using TTL compatible family e.g. HCT Can directly drive TTL Applications: CMOS/TTL interfacing VOHMIN, VOLMAX VIHMIN, VILMAX 3.5 VOHMIN, VOLMAX VIHMIN, VILMAX 4.9 2.0 2.7 1.5 0.5 TTL CMOS 0.8 0.1 CMOS TTL 5. Applications: Unused inputs Floating inputs can lead to unreliable operation!!! Unused (Floating) Inputs [] Tie together and bundle with used inputs OR [] Tie HIGH thru pull up resitor, Rpu OR Must ensure that [] Tie LOW thru pull down resistor, Rpd does not affect [] For CMOS use 1K-10K values design function. [] For TTL calculate based on # of inputs tied thru E.g. tie HIGH for AND/NAND or resistor so that: LOW for Vcc-RpuIIHmax > VIHmin OR/NOR RpdIILmax < VILmax []Too small Rpu makes TTL susceptible to spikes etc. over 5.5V. See Sec 3.10.4, 3.5.6 Wake. Power supply filtering • For each logic IC place a small capacitor (0.01uF tp 0.1uF) across Vcc and ground in close proximity to the IC • Reduces transient effect of switching on power supply, particularly when supply source is connected via long circuit path (resistive and inductive effects). Essentially each capacitor provides a local reservoir for fast supply of charge required when the device switches Applications: Open-drain (CMOS) or open collector (TTL) outputs • In CMOS no PMOS transistor, use external pull-up resistor for Vcc drive Vcc Calculate external Rpu so that VOLMAX achieved at IOLMAX. Must include other loads so this gives minimum Rpu. Vcc Rpu IC Z A Q1 B Q2 A 0 0 1 1 B 0 1 0 1 Q1 open open ON ON Q2 open ON open ON Output stage of Open Drain NAND Z 1 1 1 0 Why ? • Slightly higher current capability • Can form an open-drain/collector bus. Can select data for access to common bus.. E.g for Dataout = Datai set Enablej =0, jI, Enablei =1, Problem -- really bad rise time due to all O/P capacitances in parallel and large pullup. Applications: Bus Access - Contention and Tristate Logic Common bus 0 a Best “fix”….Tristate logic Vin 1 Vout EN 1 b 0 ?? “regular TTL or CMOS •Get bus contention when two outputs try to drive the bus to different states. • Value on the bus may be indeterminate; •Damage possible (a driving b!!) •On a PC data bus, can cause PC to crash EN 0 1 1 Vin x 1 0 Vout HiZ 0 1 •Available in inverting or non-inverting .. Sec 3.7.3 Wakerly. •NO Pull-up needed •NO degradation in transition speed Applications: Digital meets analog Schmitt Trigger Inputs…Sec3.7.2/Wakerly • Schmitt trigger devices are used primarily to deal with signal levels which are not at valid logic levels. They can therefore be used for • interfacing noisy analogue signals to a logic circuit e.g. signals from switches, RC networks etc. • interfacing slow signals (i.e. signals which remain in the invalid range for relatively long periods) • regenerating degraded logic signals e.g. signals on a long serial communication line. Schmitt trigger devices do comply with the input thresholds of the respective family. However, they employ a bit of hysterisis (memory!!) to take care of invalid signal levels. The devices are characterised by upper and lower thresholds (UT, LT). When the input exceeds UT it is treated as a logic 1 UNTIL it goes below LT. Then, and only then, is it treated as a logic 0. Vo Vi Vo LT Vo UT Last level is latched until opposite threshold is crossed VL VH Vi Schmitt Trigger o/p Characteristic VT Vi Standard logic o/p Characteristic Applications: Logic Drive Driving a LED with TTL Vcc ILED R VLED Logic Device VOL Low output turns LED ON Drive current typ 5 -10mA Use buffers for extra drive • ILED is 10mA typically worst case • Use formula: VOL+VLED+(ILED*R)=VCC to determine R. NB……. • Can assume worst case VOL=VOLMAX for some CMOS as well as TTL at IOL=ILED. • Best to use device for which IOLMAX>ILED. Applications: Logic Drive Driving a Solenoid or relay with TTL Vcc Free-wheeling diode protects electronics from coil back emf Logic Device Low output turns activates relay or solenoid • 5V relays do exist. • Some incorporate the free wheeling Diode. • Most have enough internal resistance to operate directly as shown. • Check using LED computation if built in resistance is sufficient or if an external series resitance is needed