Review Slides

advertisement

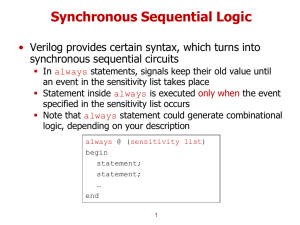

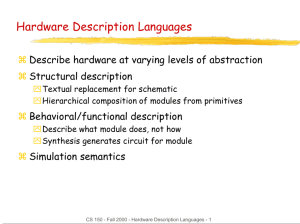

ECE 551 Digital System Design & Synthesis Fall 2011 Midterm Exam Overview Exam Details Midterm October 18th, 7:15pm, 1800EH Closed book/notes, except 8.5 x 11 sheet (both sides) No electronic devices Everything covered through week 5 Homework 1-4, all assigned readings Example midterms available in Learn@UW Review session in discussion 2 Midterm Warnings [1] Just about anything in the course is fair game Lectures, IEEE standard, “Nonblocking Assignments in Verilog Synthesis” This review is not comprehensive Review your homework, lecture notes, and practice midterms 3 Midterm Warnings [2] Allowed 1 sheet (8.5x11) of notes – can write on both sides Pen or pencil (bring more than one) Not Allowed Cheating Talking/whispering/pointing Leaving the room during the exam Use of any PDAs, calculators, cell phones, etc. Textbooks, documents beyond the 1 sheet allowed above 4 Things To Know [1] Verilog Syntax Types of Verilog Structural RTL Behavioral Structural Instantiation vs. declaration Naming instances Port connections by signal order vs. port names RTL Verilog (Continuous Assignments) Operators, bit lengths, delays 5 Things To Know [2] Variables and Nets Differences between them How to declare each How to declare vectors How to declare register files / memories When do you use reg and when do you use wire? Number Representation Base notation # of bits Handling of x and z in operations Unsigned values are zero extended 6 Things To Know [3] Behavioral constructs initial, always case, casex, casez, if, else if, else, for Use of defaults (else, default case) and why Procedural assignments (blocking vs. non-blocking) Combinational vs. sequential Triggers for always blocks (combinational/sequential) Synchronous/asynchronous reset Timing control @, #, posedge, negedge Inter- and intra-assignment delays 7 Things To Know [4] Testbenches Instantiating UUT (unit-under-test) Generating a clock properly Providing stimulus Exhaustively for small problems Important and representative cases for larger problems Test all FSM transitions and outputs $display, $monitor, $strobe 8 Things To Know [5] Good practices for Verilog writing Don’t mix blocking / non-blocking Blocking for combinational, non-blocking for sequential Don’t write self-triggering loops No cyclic combinational logic or latch inference Don’t assign to a variable in more than one block Add comments to your code 9 Things To Know [6] Finite State Machines Explicit vs. implicit Moore vs. Mealy, and how they’re coded Use of localparam to define state values Combinational vs. sequential State register Combinational logic to determine next state Combinational logic to determine outputs Verilog Stratified Event Queue What it means for blocking vs. non-blocking What it means for $display vs. $strobe 10 Suggestions On notes have one (or more) example of each of the topics covered (if you’re not comfortable with them) At worst, take directly from slides/book/standard Can put this on one side of sheet (small font), leave other side for your own notes, additional examples. Do not depend on notes for EVERYTHING Fast and easy – but not terribly effective. Won’t finish test in time! Are just intended for help with syntax, etc. 11 Review Questions Why is it useful to include a default item in a case statement? Write behavioral code for a 3-bit counter with asynchronous reset and the following interface count_3bit(output reg [2:0] count, input reset, clk); Write behavioral code for a 4-bit leading zero detector with the following interface lzd_4bit(output reg[1:0] pos, input [3:0] A); The output should indicate the number of leading 0s in A. Assume A is non-zero. 12 Review Question Answers module count_3bit(output reg [2:0] count, input reset, clk); always @(posedge clk, posedge reset) if (reset) count <= 0; else count <= count+1; endmodule 13 Review Question Answers module lzd_4bit(output reg [1:0] pos, input [3:0] A); always@ (A) begin casez(A) 4'b0001: pos = 2’d3; 4'b001?: pos = 2’d2; 4'b01??: pos = 2’d1; 4'b1???: pos = 2’d0; default: pos = 2'bx; endcase end endmodule 14 Review Question Answers module lzd_4bit(output reg [2:0] pos, input [3:0] A); always@ (A) begin casez(A) 4'b0000: pos = 3’d4; 4'b0001: pos = 3’d3; 4'b001?: pos = 3’d2; 4'b01??: pos = 3’d1; 4'b1???: pos = 3’d0; default: pos = 3'bx; endcase end endmodule 15 Review Questions What does the following piece of code do? Is it synthesizable? module circuit (output reg [7:0] count, input [7:0] datain, input load, clk); always@(posedge clk) begin if (load) begin for (count = datain; count > 0; count = count - 1) @(posedge clk); end end endmodule Note: @(event) waits until event occurs. 16 Review Questions Determine when each expression is evaluated and assigned, and the value it is assigned. always @(*) begin #2 b = a + a; c = #3 b + a; end always @(posedge clk) begin d <= #2 c + a; c <= #2 d + a; end initial begin a = 3; b = 2; c = 1; d = 0; clk = 1; end 17 Review Questions Determine the console output. always @(posedge clk) begin d <= #2 c + a; $strobe (“s %t %b %b”, $time, c, d); $display (“d %t %b %b”, $time, c, d); c <= #2 d + a; end initial begin a = 3; c = 1; d = 0; clk = 1; end $monitor(“m %t %b %b”, $time, c, d); 18 Review Questions Write behavioral code for a 4-bit pattern detector with the following interface; ptrn_4bit(output reg det, input [3:0] pattern, input sd, reset, clk); Serial data comes in on sd. Implement as a Moore machine with synchronous reset, and detect all pattern instances (instances may overlap). 19