Unit 4 PowerPoint Slides

advertisement

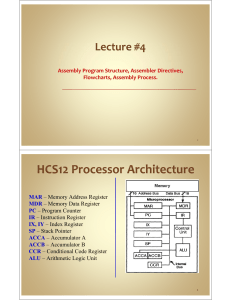

EET 2261 Unit 4 Arithmetic Instructions; Branching & Iteration Read Almy, Chapters 7 and 8. Homework #4 and Lab #4 due next week. Quiz next week. Addition Instructions • These are self-explanatory, except the two instructions that add with carry. These are for multibyte addition. See next slide. (Table from p. 59 of the HCS12 CPU Reference Manual.) Multi-Byte Addition • Suppose we want to do this addition and store the result at memory location $1000: $2162 + $33C3 • Each of our operands is two bytes long. Since Accumulator A can only hold one byte, we can’t do: LDAA #$2162 ADDA #$33C3 STAA $1000 • But we can do it by breaking it down into two halves, as shown on next slide. Adding with Carry • To add $2162 plus $33C3, use a two-step process: 1. Add the low-order bytes ($62 plus $C3) and store the result at $1001. 2. Then add the high-order bytes ($21 plus $33), remembering whether there was a carry from the previous step. For this we use the ADCA instruction. Store this result at $1000. LDAA #$62 ADDA #$C3 STAA $1001 LDAA #$21 ADCA #$33 STAA $1000 Extending the Idea • The previous example showed how to add two twobyte numbers. We can extend the idea to numbers of any length. • Example: $12345678 + $9ABCDEF0 • We’d add the lowest-order bytes ($78 + $F0) using ADDA, then add the higher-order bytes using three ADCAs. Subtraction Instructions • Again, these are self-explanatory, except the two instructions that subtract with borrow, which are for multi-byte subtraction. (Note that C, the “carry bit,” acts as a borrow bit when we’re subtracting.) (Table from p. 59 of the HCS12 CPU Reference Manual.) Decrement and Increment Instructions (Table from p. 61 of the HCS12 CPU Reference Manual.) • Caution: INCA and ADDA #1 give the same result in A, but these two instructions do not affect the CCR in the same way. Negate Instructions (Table from p. 63 of the HCS12 CPU Reference Manual.) Multiplication Instructions • When multiplying, the register holding the result must be twice the size of the registers holding the operands. • Example: With 8-bit unsigned operands, the biggest multiplication is 255 × 255, which equals 65,025 (or %1111 1110 0000 0001). • Below, Y : D means Y and D combined together, which is 32 bits. (Table from p. 64 of the HCS12 CPU Reference Manual.) Quotient and Remainder •We know that 7 ÷ 2 = 3.5 •Recall that another way to say this is that 7 ÷ 2 = 3 with a remainder of 1. •In this example, 3 is called the quotient and 1 is called the remainder. •The HCS12’s division instructions give us answers like “3 with a remainder of 1,” not “3.5”. •Another example: If you take 20÷8, what is the quotient and what is the remainder? Division Instructions • We’ll ignore FDIV, which does fractional division; the other four division instructions are similar to each other, since they all do integer division. (Table from p. 64 of the HCS12 CPU Reference Manual.) Logical Shift Instructions • These instructions shift in a 0 on end, and shift out to the Carry bit on the other end. (Table from p. 66 of the HCS12 CPU Reference Manual.) Arithmetic Shift Instructions • The arithmetic shifts left are identical to the logical shifts left. (For instance, ASL is identical to LSL.) But the arithmetic shifts right are different from the logical shifts right. (Table from p. 66 of the HCS12 CPU Reference Manual.) Rotate Instructions • The rotate instructions are similar to the logical shift instructions, except the rotate instructions “wrap around” the Carry bit from one end to the other end. (Table from p. 66 of the HCS12 CPU Reference Manual.) Review: Representing Numbers • We have several common methods for representing numbers in digital systems. • Standard binary representation, which comes in two “flavors”: • Unsigned binary • Signed binary • Binary-coded decimal (BCD) representation, which also comes in two “flavors”: • Unpacked BCD • Packed BCD • ASCII representation Standard Binary Representation • Standard binary representation is the most efficient (uses the least memory and is the fastest to operate on). • We use unsigned binary representation when we know that the range of numbers we’re dealing with does not include negative numbers. • We use signed binary representation when the numbers we’re dealing with may be positive or negative. Negative numbers are represented in two’s-complement form. Binary-Coded Decimal (BCD) Representation • Devices such as digital clocks that display numbers in human-readable form often use BCD representation. • In unpacked BCD, each byte holds a single digit. Example: 47 is represented as 0000 0100 0000 0111 • In packed BCD, each byte holds two digits. Example: 47 is represented as 0100 0111 ASCII Representation • ASCII is a widely recognized standard that is often used for transferring data between different programs or devices. • Example: 47 is represented as 0011 0100 0011 0111. Review: Same Number, Different Representations • We have several different ways of representing the number 47: • In standard binary representation (signed or unsigned), it’s 0010 1111 • In unpacked BCD, it’s 0000 0100 0000 0111 • In packed BCD, it’s 0100 0111 • In ASCII, it’s 0011 0100 0011 0111 The DAA Instruction • To add binary-coded decimal (BCD) operands: 1. Add them using ABA, ADCA, or ADDA. 2. Then immediately execute the Decimal Adjust A (DAA) instruction. • The DAA instruction examines the Condition Code Register’s H bit to decide how the addition result needs to be adjusted. Compare and Test Instructions • Compare and test instructions perform a subtraction but don’t save the result anywhere. • They’re useful because they set the CCR bits based on the result. A compare or test is usually followed by a branch instruction that looks at the CCR bits. (Table from p. 62 of the HCS12 CPU Reference Manual.) Flowcharts •A flowchart is a diagram that shows the logic of a computer program. (See pages 41-42 of textbook.) •Arrows show the flow of the logic. •A diamond represents a decision point, with alternate paths based on the decision. Read Temperature Temp > 70? No Turn on LED 1 Yes Turn on LED 0 Straight-Line Structure •The programs we’ve studied up to now had a straight-line structure, with no decision points. •Instructions executed in order from start to finish. Start Action 1 Action 2 . . . Action n End Straight-Line Structure: Example Flowchart Start Load 5 into A Add 17 to A Program ABSENTRY Entry ORG $2000 Entry: LDAA #05 ADDA #17 Load 3 into B LDAB #03 Increment A INCA Decrement B DECB Add $1A to B ADDB #$1A END End Review: Program Counter • How does the HCS12 keep track of where it is in a program? That’s the job of the program counter (PC), a 16-bit register that points to the address of the next instruction to be executed. • Each time an instruction is executed, the PC is automatically increased by the size of this instruction (a number from 1 to 5) so that the PC now points to the next instruction in memory. Program Counter: Example PC $2007 $2006 $2004 $2002 $2000 • Initiallythe While PCADDA LDAA LDAB INCA = $2000, isis isbeing being being pointing executed, executed, executed, to thePC PC PC LDAA. ===$2007, $2002, $2006, $2004,pointing pointing pointingto to tothe the theDECB. ADDA. INCA. LDAB. “Forever” Loop Structure •Often we want a program to contain an endless loop, in which we keep repeating the same action(s) over and over again forever. . . . Action Branch Instructions • To program the “forever” loop shown on the previous slide, we use a branch instruction. • As we’ll see, the HCS12 has more than 30 different branch instructions. • Branch instructions can change the default order of execution by forcing the program counter to point to an instruction other than the next one in memory. Branch Always (BRA) • The branch instruction that we need for our “forever” loop is Branch Always (BRA). • It’s the simplest branch instruction, because it always branches. • We’ll soon study other branches that check a condition and then, depending on that condition, may or may not branch. • These other branches are often called conditional branches, while BRA is an unconditional branch. “Forever” Loop Structure: Example Flowchart Program ABSENTRY Entry Start ORG $2000 Load A from $1000 Entry: Increment A LDAA $1000 GoHere: INCA BRA GoHere END Review: Addressing Modes • The HCS12’s six addressing modes are: • Inherent • Immediate • Direct • Extended • Indexed (which has several variations) • Relative • We’ve studied the first four and briefly looked at the fifth. Now we need to understand relative addressing mode. Relative Addressing Mode • Relative addressing mode is used only by branch instructions. • In this addressing mode, the opcode is followed by an offset, which is a two’scomplement number (positive for branching forward in a program, negative for branching backwards). • Example: In the previous program, BRA GoHere in assembly language translates into $20 FD in machine code. The offset, $FD, is −3 in two’s complement notation. Using Labels with Branch Instructions • Figuring out the offset can be a tedious chore. • Fortunately, the assembler lets you use labels instead to specify the branch destination; then the assembler figures out the offset. A Self-Pointing Branch • We saw in Lab #2 that BRA * is a selfpointing branch instruction. • The assembler treats BRA * as being the same as the following instruction: GoHere: • BRA GoHere It’s useful as a way of stopping a program that has finished its task. Otherwise the processor would try to continue past the end of your program, executing whatever instructions happen to be located in memory after your program. A Self-Pointing Branch: Example Program ABSENTRY Entry Start ORG $2000 Load A from $1000 Entry: LDAA $1000 GoHere: BRA GoHere END Conditional Structure •Often we want to check some condition and then either perform an action or skip the action, depending on whether the condition is true or false. . . . Yes Condition? No Action . . . Branch Instructions and the CCR • Most branch instructions examine one or more of the flag bits in the Condition Code Register (CCR) to decide whether to continue with the next instruction in memory or jump to a different instruction. Simple Branch Instructions • The simple branch instructions examine a single bit in the CCR. Mnemonic Function Condition Checked (Table from p. 74 of the HCS12 reference manual.) Repeating an Action Many Times •Often we want to perform an action several times. The brute-force way to do this is by using a straight-line program in which we repeat the same instruction the correct number of times. Start Do the action Do it again . . . Do it again End Brute Force Method: Example Start ABSENTRY Entry Load A from $1000 Increment A Increment A Increment A Increment A Increment A Store A to $1001 End ORG $2000 Entry: LDAA $1000 INCA INCA INCA INCA INCA STAA $1001 END Counted Loop Structure Start •A better way is to use a counted loop, as shown here. Initialize Counter Do the action Decrement Counter No Counter = 0? Yes End Counted Loop Structure: Example Start Load A from $1000 Counter=5 ABSENTRY Entry ORG $2000 Entry: LDAA $1000 LDAB #5 ;Init. Counter Increment A Decrement Counter No Counter = 0? Yes Store A to $1001 End Again: INCA ;Do action DECB ;Dec. Counter BNE Again ;Counter=0? STAA $1001 END Time Delay Loops • Counted loops are often used to introduce time delays. The idea is that we just spin around and around in a counted loop, wasting time. • Example: . . . LDAB #255 Again: DECB BNE Again . . . ;Doing some stuff. ;Waste some time. ;Do more stuff. Calculating the Time Delay • We can calculate the approximate delay by knowing the microcontroller’s cycle time (in our case, 41.7 ns) and how many cycles are required to execute each instruction. • Example: LDAB #255 Again: DECB BNE Again • Number of cycles 1 1 +3 4 × 255 = 1020 1021 Total delay 1021 × 41.7 ns 42.5 µs How to Get Longer Delays? • • The previous timing loop gave us a delay of only about 42 µs. Here three ways to get longer delays: • Use a 16-bit register such as Index Register X instead of the 8-bit Accumulator B. • Place more instructions inside the loop. • Use nested loops. All three techniques are used on the next slide. Nested Timing Loops • If a single loop doesn’t give us a long enough delay, we can use nested loops (a loop inside a loop) to waste even more time! • Example: Loop2: Loop1: LDAB #10 LDX #$FFFF DEX NOP BNE Loop1 DECB BNE Loop2 Inner Loop Outer Loop Short Branches • In short branch instructions, the offset is an eight-bit signed number. • So the offset can range from 128 to +127. • Older microcontrollers only had short branch instructions, limiting how far away you could branch. • All of the branch instructions we’ve discussed (and others that we’ll discuss next week) are short branch instructions. See next slide. Short Branch Instructions (Table from p. 74 of the HCS12 CPU Reference Manual.) Is This a Problem? • Is it a problem that the offset can range only from 128 to +127? • Not in short programs, but it can be in long programs. . . . BEQ GoHere . . . GoHere: STAA $1001 Suppose there are a few hundred instructions between the BEQ and the STAA. That’s too far away! You’ll get an error when you try to assemble the program. Long Branches • The HCS12 also has long branch instructions, in which the offset is a sixteenbit signed number. • So the offset can range from 32,768 to +32,767, letting us branch to any other location in the HCS12’s 64K memory space. • There’s a long-branch version of each short branch instruction. See next slide. Long Branch Instructions (Table from p. 75 of the HCS12 CPU Reference Manual.) Jump • The Jump (JMP) instruction is similar to BRA or LBRA. It forces the program to jump to a new instruction by loading a value into the Program Counter. • While BRA and LBRA use relative addressing mode, JMP uses extended or indexed addressing. • Example: JMP $2050 causes $2050 to be loaded into the Program Counter, so that the instruction located at that address will be executed next.