l02

advertisement

F28PL1 Programming Languages

Lecture 2: Assembly Language 1

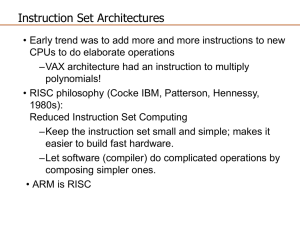

CISC & RISC

•

•

•

•

CISC: complex instruction set computer

original CPUs very simple

poorly suited to evolving high level languages

extended with new instructions

– e.g. function calls, non-linear data structures, array bound

checking, string manipulation

• implemented in microcode

– sub-machine code for configuring CPU sub-components

– 1 machine code == > 1 microcode

• e.g. Intel X86 architecture

CISC & RISC

• CISC introduced integrated combinations of features

–

–

–

–

e.g. multiple address modes, conditional execution

required additional circuitry/power

multiple memory cycles per instruction

over elaborate/engineered

• many feature combinations not often used in practise

• could lead to loss of performance

• better to use combinations of simple instructions

CISC & RISC

• RISC: reduced instruction set computer

• return to simpler design

• general purpose instructions with small number of

common features

– less circuitry/power

– execute in single cycle

• code size grew

• performance improved

• e.g. ARM, MIPS

ARM

• Advanced RISC Machines

• UK company

• originally Acorn

– made best selling BBC Microcomputer in 1980s

• world leading niche processors

– 2009: 90% of all embedded processors

– mobile phones, media players, games, peripherals etc

– e.g. Nokia, iPod, iPad, Blackberry, Nintendo

ARM

• 32 bit RISC processor architecture family

• many variants

• general reference in library:

– W. Hohl, ARM Assembly Language, CRC Press, 2009

– ARM7TDMI

• ARM does not make chips

• licences the IP core (intellectual property) logic

design to chip manufacturers

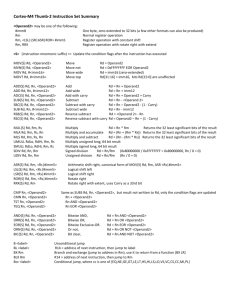

Cortex-M3

• ARM CPU in STM32-Discovery board

• Thumb2 instruction set

– based on ARMV7

– subset of full ARM instructions

– 16 bit length instructions

• Cortex-M3 manual

• http://infocenter.arm.com/help/topic/com.arm.doc.dui05

52a/DUI0552A_cortex_m3_dgug.pdf

MDK-ARM

• ARM development environment for:

– C & assembler

– many ARM-based systems

• includes simulator

• free restricted download via:

• http://www.keil.com/arm/mdkbasic.asp

• MDK-ARM/Cortex-M3 guide

• http://www.st.com/internet/com/TECHNICAL_RESOURCES

/TECHNICAL_LITERATURE/USER_MANUAL/CD00283786.pd

f

Cortex-M3 memory map

• linear 4GB address

space

• modified Harvard

architecture in CPU

0.5GB

1GB

0xFFFFFFFF

Vendor Specific

External Peripheral Bus 0xE0100000

Internal Peripheral Bus 0xE0040000

0xE0000000

External Device

0xA0000000

1GB

External RAM

0.5GB

Peripheral

0.5GB

SRAM

0x60000000

0x40000000

0x20000000

0.5GB

Code

0x00000000

Memory

• linear addressing

• 2 descending stacks

– main stack

– process stack – used by OS

• all operations based on registers

• must move data between registers & memory

Registers

• 16 * 32 bit registers

• working registers

– R0-R7 – low registers

– R8-R12 – high registers

• R13 – stack pointer (SP)

• R14 - link register (LR)

• R15 – program counter (PC)

• PSR – program status register

– bits for negative (N), zero (Z), carry (C), overflow (V)

Data formats

• word

– 32 bits

– long

• half word

– 16 bits

– int

• byte

– 8 bits

– char

Programming approach

• in high level programming:

– identify variables & types

– compiler maps these to memory & data representation

– use of memory v registers invisible

• in low level programming

– must make explicit use of memory & registers

– must choose data representation

• registers much faster than memory

• try to map variables to registers

• what if more variables than registers...?

Example: sum of 1st 10 integers

• we write:

• C compiler generates:

#define MAX 11

int s;

int n;

n = 0;

while(n<MAX)

{ s = s+n;

n = n+1;

}

MOVS

MOVS

B

LOOP ADD

ADDS

TEST CMP

BLT

r2,#0x00

r1,#0x00

TEST

r2,r2,r1

r1,r1,#1

r1,#0x0A

LOOP

Example: sum of 1st 10 integers

• we write:

• C compiler generates:

#define MAX 11

int s;

int n;

n = 0;

while(n<MAX)

{ s = s+n;

n = n+1;

}

MOVS

MOVS

B

LOOP ADD

ADDS

TEST CMP

BLT

r2,#0x00

r1,#0x00

TEST

r2,r2,r1

r1,r1,#1

r1,#0x0A

LOOP

Example: sum of first 10 integers

• s == r2 - register 2

• n == r1 – register 1

MOVS

r2,#0x00

• move hexadecimal constant 0x00 to register 2

• set condition code flags

MOVS

r1,#0x00

• move hexadecimal constant 0x00 to register 2

• set condition code flags

B

TEST

• branch to label TEST

Example: sum of first 10 integers

LOOP ADD

r2,r2,r1

• label LOOP

• put in r2 sum of r2 and r1

ADDS

r1,r1,#1

• put in r1 sum of r1 and decimal constant #1

• set condition code flags

Example: sum of first 10 integers

TEST CMP

r1,#0x0A

• label TEST

• compare r1 and hexadecimal constant #0x0A == 10

• set condition code flags

BLT

LOOP

• branch to label LOOP if flags indicate “less than”

Instruction format

mnemonic operands

– general format

– operands depend on instruction

mnemonic

– meaningful short form

– reminds us what instruction does

• ARM uses {...} for options

• Rd or Rm == register -r0..r15

Operands

• first operand usually rd

• Operand2 == flexible 2nd operand

– constant

– Rm

• constant == 8 hexadecimal digits

• constant == decimal

– size of decimal depends on instruction

• #imm16 == 0-65535 == 16 bit

MOV: move

MOV Rd, Operand2

Rd = Operand2

• don’t update condition code flags

MOVS Rd, Operand2

• as MOV but update condition code flags

MOV Rd, #imm16

Rd = imm16

ADD: addition

ADD Rd, Rn, Operand2 Rd = Rn+Operand2

ADD Rn, Operand2 Rn = Rn+Operand2

ADDC

• add with carry

• like ADD + carry flag

ADDS/ADDCS

• like ADD/ADDC but set condition code flags

SUB: subtraction

SUB Rd, Rn, Operand2 Rd = Rn-Operand2

SUB Rn, Operand2 Rn = Rn-Operand2

SUBC

• subtract with carry

• like SUB -1 if carry flag not set

SUBS/SUBCS

• like SUB/SUBC but set condition code flags

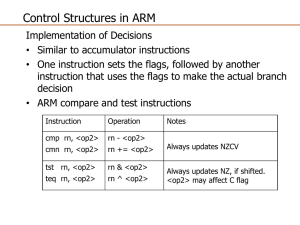

CMP: compare

CMP Rn, Operand2

• subtract Operand2 from Rn BUT ...

• ... do not modify Rn

– otherwise same as SUBS

• update Z, N, C, V flags

CMN RN, Operand2

• add Operand2 to Rn BUT ...

• ... do not modify Rn

• otherwise same as ADDS

• update Z, N, C, V flags

Flags

• N – 1 if result <0; 0 otherwise

• Z – 1 if result =0; 0 otherwise

• C – 1 if result led to carry; 0 otherwise

– i.e. X+Y > 232

– i.e. X-Y >= 0

Flags

• V – 1 if result led to overflow; 0 otherwise

• (-) == negative

• (+) == positive

– i.e. (-)X+(-)Y > 0

– i.e. (+)X+(+)Y < 0

– i.e. (-)X-(+)Y > 0

– i.e. (+X)-(-Y) < 0

B: branch

B label

• branch to label

• i.e. reset PC to address for label

Bcond label

• branch on condition to label

condition

suffix

EQ == equal

NE == not equal

CS/HS == carry set/ higher or same - unsigned

CC/LO == carry clear/lower - unsigned

MI == negative

PL == positive or 0

VS == overflow

VC == no overflow

flags

Z=1

Z=0

C=1

C=0

N=1

N=0

V=1

V=0

condition

suffix

HI == higher - unsigned

LS == lower or same - unsigned

GE == greater than or equal - signed

LT == less than - signed

GT == greater than - signed

LE == less than or equal, signed

AL == any value

flags

C=1 & Z=0

C=0 or Z=1

N=V

N!=V

Z=0 & N=V

Z=1 & N!=V

default if not

cond

Label

• identifier

• can precede any line of assembler

• represents the address of:

– instruction

– literal data

• relative to program counter (PC)

• turned into PC + offset in machine code

NOP: no operation

NOP

• do nothing

• use for padding/layout

• no cost

Layout

• ARM assembly language is layout sensitive

• must precede instruction with a tab

• for labelled instruction, use tab immediately after

label

• can’t use equivalent number of spaces

Example: multiply by adding

• m == x*y

int x;

int y;

int m;

x = 8;

y = 10;

m = 0;

while(y!=0)

{ m = m+x;

y = y-1;

}

• x == R1; y == R2; m == R3

MOV R1,#0x08

MOV R2,#0x0A

MOV R3,#0x00

LOOP CMP R2,#0x00

BEQ DONE

ADD R3,R1

SUB R2,#0x01

B LOOP

DONE NOP

Register name definition

name RN expression

• expression 0..15

• name renames the

register

e.g.

x

y

m

RN

RN

RN

1

2

3

MOV x,#0x08

MOV y,#0x0A

MOV m,#0x00

LOOP CMP y,#0x00

BEQ DONE

ADD m,x

SUB y,#0x01

B LOOP

DONE NOP

Constant name definition

name EQU expression

• name is replace with

value from expression

e.g.

x

RN 1

y

RN 2

m

RN 3

xinit

EQU 8

yinit

EQU 10

MOV x,#xinit

MOV y,#yinit

MOV m,#0x00

LOOP CMP y,#0x00

BEQ DONE

ADD m,x

SUB y,#0x01

B LOOP

DONE NOP