ln_arm_intro

advertisement

Instruction Set Architectures

• Early trend was to add more and more instructions to new

CPUs to do elaborate operations

–VAX architecture had an instruction to multiply

polynomials!

• RISC philosophy (Cocke IBM, Patterson, Hennessy,

1980s):

Reduced Instruction Set Computing

–Keep the instruction set small and simple; makes it

easier to build fast hardware.

–Let software (compiler) do complicated operations by

composing simpler ones.

• ARM is RISC

Chapter 2: The Programmer’s Model

• Concerned with the features that are available to you

from a high level, e.g.

– Where data can be stored

– What happens when the machine is given an invalid

instruction

Data Types:

• Byte:

8 bits

• Halfword:

16 bits

• Word:

32 bits

Processor Modes

ARM has seven basic operating modes:

• User:

unprivileged mode under which most tasks run

has limited access to the hardware (non-privileged)

whereas all other modes have full access (privileged) to

the CPU resources.

• FIQ:

entered when a high priority (fast) interrupt is raised

• IRQ:

entered when a low priority (normal) interrupt is raised

• Super:

entered on reset and execution of software interrupt

instruction

• Abort:

used to handle memory access violations

• Undef:

used to handle undefined instructions

• System: privileged mode using the same registers as user mode

Processor Modes

• We will mainly use User mode. Other modes much less

important for this class.

• For now, only concerned with r0-r12; treat these as

registers that can be used to store any variable.

ARM Registers

Register – internal CPU hardware device that stores binary

data; can be accessed much more rapidly than a

location in RAM

ARM has

13 general-purpose registers R0-R12

1 Stack Pointer (SP) – R13

1 Link Register (LR) – R14 holds the caller’s return address

1 Program Counter (PC) – R15

1 Current Program Status Register (CPSR)

ARM Registers

• ARM processors, with the exception of ARMv6-M and

ARMv7-M based processors, have a total of 37 or 40

registers depending on whether the Security Extensions

are implemented.

• registers are arranged in partially overlapping banks.

• There is a different register bank for each processor

mode.

• The banked registers give rapid context switching for

dealing with processor exceptions and privileged

operations.

• Additional registers are available in privileged software

execution.

ARM Registers

Additional registers in ARM processors, with the exception

of ARMv6-M and ARMv7-M, are:

2 supervisor mode registers for banked SP and LR

2 abort mode registers for banked SP and LR

2 undefined mode registers for banked SP and LR

2 interrupt mode registers for banked SP and LR

7 FIQ mode registers for banked R8-R12, SP and LR

2 monitor mode registers for banked SP and LR

6 Saved Program Status Register (SPSRs), one for each

exception mode.

The ARM Register Set

Current Visible

Visible Registers

Registers

Current

Abort

Mode

SVC

Undef

Mode

Mode

FIQ

User

IRQMode

Mode

Mode

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13 (sp)

(sp)

r13

r14 (lr)

(lr)

r14

r15 (pc)

Banked

Banked

Bankedout

out

outRegisters

Registers

Registers

User

FIQ

IRQ

SVC

Undef

r8

r9

r10

r11

r8

r9

r10

r11

r12

r13 (sp)

r14 (lr)

Abort

r12

r13 (sp)

r14 (lr)

r13 (sp)

r14 (lr)

r13 (sp)

r14 (lr)

r13 (sp)

r14 (lr)

r13 (sp)

r14 (lr)

spsr

spsr

spsr

spsr

spsr

cpsr

spsr

spsr

Processor Status Register(PSR)

Contains: Condition flags that are set by arithmetic and

logical CPU instructions and used for conditional execution

31

30

29

28

27

26

25

24

23

22

21

29

19

N Z C V Q

17

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

GE

Greater than or

equal to

Mode bits

Data

Endianness

bit

Sticky Overflow

Overflow

Carry/Borrow/Extend

Zero

Negative/Less than

Processor Status Register(PSR)

• The N, Z, C, and V bits are the condition code flags.

• Flags are set by arithmetic and logical CPU instructions

and used for conditional execution

• The processor tests these flags to determine whether to

execute a conditional instruction.

N – negative / less than

Z – zero

C – carry / borrow / extend

V – overflow

Processor Status Register(PSR)

– Q sticky overflow. set to 1 when saturation occurs

during QADD, QDADD, QSUB or QDSUB, or the result

of SMLAxy or SMLAWx overflows 32-bits

The Q flag is sticky in that, when an instruction sets it,

this bit remains set until an MSR instruction writing to

the CPSR explicitly clears it.

Instructions cannot execute conditionally on the status

of the Q flag.

Processor Status Register(PSR)

Also Contains:

• Interrupt enable/disable flags for standard (IRQ) and fast

(FIQ) interrupts.

• Thumb bit set on Thumb Instruction execution.

• Mode bits that indicate the current operating mode.

• The PSR can be accessed by the MSR or LDM

instructions.

• Each operation mode has a shadow register for the current

state of the PSR. The shadow registers are called SPSR

(saved processor status register) whereas the CPSR holds

the current state.

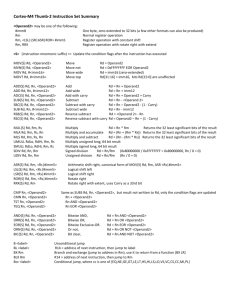

ARM Instructions

• ARM instructions are written as an operation code

(opcode), followed by zero or more operands

• Operands may be constants, registers, or memory

references

ARM Instructions

• Instruction syntax:

opcode{cond}{flags} Rd, Rn, operand2

where:

– {cond} is an optional two-letter condition, e.g. EQ

– {flags} is an optional additional flag, e.g. S

– Rd is the destination register

– Rn is the first source register

– Operand2 is a flexible second operand

• Syntax is rigid (for the most part):

–1 operator, 3 operands

–Why? Keep Hardware simple via regularity

ARM Instructions

Note:

• Operand2 is a flexible second operand to most

instructions

– it is passed through the barrel shifter (a functional

unit that can rotate and shift values)

– it can take one of three forms:

o Immediate value: an 8-bit number rotated right

by an even number of places

o Register shifted by a value: a 5-bit unsigned

integer shift.

o Register shifted by a register: the bottom 8 bits

of a register.

ARM Instructions

Examples of Operand2

• Immediate values

o add r0, r1, #3

o mov r0, #15

o mov r1, #0x12

• Register shifted by a value

o mov r0, r1, lsl #4

o orr r1, r1, lsr #10

• Register shifted by a register

o cmp r1, r2, lsl r0

o add r5, r3, ror r0

ARM Comments

• One way to make your code more readable is to use

comments!

• The at symbol, @, is used for ARM comments in

QEMU

–anything from @ to end of line is a comment and

will be ignored

• The block comment, /* comment */, is also available

Immediates

• Immediates are numerical constants.

• They appear often in code, so there are ways to

indicate their existence

• Add Immediate:

/* f = g + 10

(in C)

*/

ADD r0, r1, #10 @ (in ARM)

where ARM registers r0, r1 are associated with C

variables f, g

• The second operand is a #number instead of a

register.

Move instructions

• mov Rd

• mvn Rd

Operand2

0xFFFFFFFF EOR Operand2

• Examples

mov r0, #15

mov r0, r1

Compare instructions

• cmp – compare

o Flags set to result of (Rn – Operand2)

• cmn – compare negative

o Flags set to result of (Rn + Operand2)

• tst – bitwise test

o Rd := Rn or Operand2

• teq – test for equivalence

o Rd := Rn and not Operand2

Compare instructions

• Comparisons produce no results – they just set condition

codes.

• Ordinary instructions will also set condition codes if the

“S” bit is set. The “S” bit is implied for comparison

instructions.

• Examples of compare instructions

cmp r0, r1

cmp r0, #10

tst r1, #1

teq r0, 41

Logical instructions – Chapter 7 (pp 97 – 98)

•

•

•

•

and – logical and

eor – exclusive or

orr – logical or

bic – bitwise clear

• Examples

and r2, r0, r1

eor r2, r2, #1

Rd

Rd

Rd

Rd

Rn and Operand2

Rn eor Operand2

Rn or Operand2

Rn and not Operand2

@ r2 = r0 & r1

@ r2 = r0 ^ 1

Arithmetic instructions (p. 104)

•

•

•

•

•

•

add

adc

sub

sbc

rsb

rsc

Rd

Rd

Rd

Rd

Rd

Rd

Rn + Operand2

Rn + Operand + Carry

Rn – Operand2

Rn – Operand2 – not(Carry)

Operand2 – Rn

Operand2 – Rn – not(Carry)

• Examples

add r2, r0, r1

sub r2, r0, r1

@ r2 = r0 + r1

@ r2 = r0 – r1