Lecture 3

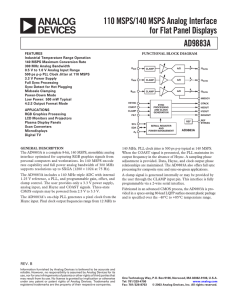

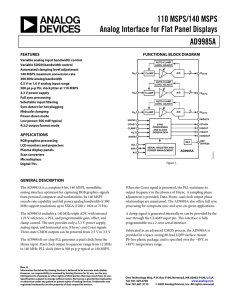

advertisement

COMP541 Video Monitors Montek Singh Oct 1, 2014 1 Outline Last Friday’s lab Tips/discussion How to generate video signal 2 How about making a BCD stop watch? Each digit counts 0 to 9, and then wraps around i.e., display is decimal number, not hex Do the following: Separate the 16-bit number into four 4-bit numbers reg [3:0] A3, A2, A1, A0; For A0: on each clock tick… – if this digit is 9, change it to 0, else add 1 to it For A1, A2, A3: on each clock tick… – if all lower A’s are at 9, then » if this digit is 9, change it to 0, else add 1 to it – else this digit does not change Slow it down to tick once per 1/100 second have a separate counter to count 220 clock ticks (~1/100th sec) update the 4-digit number only whenever this counter fills up! 3 Reminder: Good Verilog Practices Best to use single clock for all FFs Make all signals synchronous to one clock No: @(posedge button) etc. Yes: @(posedge clock) Avoids “weird” and frustrating problems Multiple modules Tested individually Top level has input and outputs One module per file Just to make it easier to follow and test 4 VGA Monitors 5 How Do Monitors Work? Origin is TV, so let’s look at that LCDs work on different principle, but all signaling still derived from TV of 1940s Relies on your brain to do two things Integrate over space Integrate over time 6 Many Still Images Video (and movies) are a series of stills If stills go fast enough your brain interprets as moving imagery 50-60 Hz or more to not see flicker – “1 Hz” means once per second In fact, even if the scene does not change… … a single “still” image is displayed repeatedly over time Why? Phosphor persistence varies 7 Cathode Ray Tube (CRT) From wikipedia: http://en.wikipedia.org/wiki/Cathode_ray_tube 8 Deflection Coils 9 Simple Scanning TV Electron beam scans across Turned off when Scanning back to the left (horizontal retrace ----) Scanning to the top (vertical retrace ____) 10 Scanning: Interlaced vs. Progressive (Some) TVs use interlacing Every other scan line is swept per field Two fields per frame (30Hz) Way to make movement less disturbing Computers use progressive scan Whole frame refreshed at once 60Hz or more, 72Hz looks better Similar notation used for HD i = interlaced (1080i) p = progressive (1080p) which better? 11 Color Three colors of phosphor three beams, one each for the three phosphors Black: all beams off White: all beams on Picture is a bit misleading. Mask (or aperture grill) ensures beams hit only correct color phosphor. 12 What about LCD? How do LCD monitors work? internals are very different no beams, tubes made up of tiny LCD cells However, external signaling is the same! for compatibility Same goes for micro-mirror projectors 13 VGA Signaling ual Timing signals horizontal sync (hsync) & vertical sync (vsync) tus byte YS XY YY P X direction byte 1 0 Y direction byte X0 X1 X2 X3 X4 X5 X6 X7 P 1 0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 P 1 Color values: R, G, B Mouse Data Format total 8 bits for Nexys 3 (rrrgggbb), 12 bits for Nexys 4 (rrrrggggbbbb) Stop bit Start bit s 10 FPGA signals to 8-bit color and the two (HS – Horizontal Sync, c). The color signals use that work in conjunction nation resistance of the eight signal levels on the gnals, and four on blue sensitive to blue levels). gure 13, produces video eed in equal increments and 0.7V (fully on). Using nt colors can be h unique 8-bit pattern. A must be created in the c and color signals with der to produce a working e specified, published, y the VESA organization ollowing VGA system ovided as an example of ght be driven in 640 by recise information, or for Stop bit Start bit 5 1 10 Stop bit Idle state Pin 1: Red Pin 2: Grn Pin 3: Blue Pin 13: HS Pin 14: VS 6 15 11 RED0 2K RED1 1K RED2 510 P8 T6 V6 GRN0 2K GRN1 1K GRN2 510 R7 T7 BLU1 1K BLU2 510 U7 V7 N7 N6 P7 Pin 5: GND Pin 6: Red GND Pin 7: Grn GND Pin 8: Blu GND Pin 10: Sync GND digital to analog converter RED GRN HSYNC 100 VSYNC 100 Spartan 6 Nexys 3 BLU HS VS HD-DB15 Nexys 4 14 VGA Timing You supply two pulses hsync and vsync allow the monitor to lock onto timing One vsync per frame One hsync per scan line hsync does not stop during vsync pulse Image from dell.com 15 Horizontal Timing Terms Horizontal timing: hsync pulse Back porch (left side of display) Active Video Video should be blanked (not sent) at other times Front porch (right side) Picture not accurate for our case; just for illustration. Video and HSYNC not on same wire 16 Horizontal Timing 640 Horizontal Dots Horiz. Sync Polarity NEG Scanline time (A) 31.77 us Sync pulse length (B) 3.77 us Back porch (C) 1.89 us Active video (D) 25.17 us Front porch (E) 0.94 us This diagram shows video as a digital signal. It’s not – video is an analog level. us = microsecond Image from http://www.epanorama.net/documents/pc/vga_timing.html 17 Vertical Timing (note ms, not us) Vert. Sync Polarity NEG Vertical Frequency 60Hz Total frame time (O) 16.68 ms Sync length (P) 0.06 ms Back porch (Q) 1.02 ms Active video (R) 15.25 ms Front porch (S) 0.35 ms 18 Timing as Pixels Easiest to derive all timing from single-pixel timing How “long” is a pixel? Active video / number of pixels 25.17 us / 640 = 39.32ns Conveniently close to 25 MHz – just use that Actual VESA spec is 25.175 MHz 19 Standards 640 x 480 (sometimes x 60Hz) is “VGA” I will give you spec sheets in lab You can try for 800x600 at 60 Hz (40 MHz exactly) or 800x600 at 72 Hz (50 MHz exactly) Note that some standards have vsync and hsync positive true, some negative true choose correct polarity determine by experimentation! 20 Color Depth Nexys3 Reference Manual Voltage of each of RGB determines color Nexys 3: 1 0 L R 0 1 XS YS XY YY Mouse status byte X direction byte P 1 0 Y direction byte X0 X1 X2 X3 X4 X5 X6 X7 P 1 0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 P bit Start blue bit 3-bit for red Start and 2-bit for Stop bit bit green, Stop Start bit Idle state Nexys 4: 1 Stop bit Idle state Mouse Data Format 4-bit for red, green and blue VGA Port All on for white The Nexys3 board uses 10 FPGA signals to create a VGA port with 8-bit color and the two standard sync signals (HS – Horizontal Sync, and VS – Vertical Sync). The color signals use resistor-divider circuits that work in conjunction with the 75-ohm termination resistance of the VGA display to create eight signal levels on the red and green VGA signals, and four on blue (the human eye is less sensitive to blue levels). This circuit, shown in figure 13, produces video color signals that proceed in equal increments between 0V (fully off) and 0.7V (fully on). Using this circuit, 256 different colors can be displayed, one for each unique 8-bit pattern. A video controller circuit must be created in the FPGA to drive the sync and color signals with the correct timing in order to produce a working display system. VGA System Timing 5 Pin 1: Red Pin 2: Grn Pin 3: Blue Pin 13: HS Pin 14: VS 1 10 6 15 11 RED0 2K RED1 1K RED2 510 P8 T6 V6 GRN0 2K GRN1 1K GRN2 510 R7 T7 BLU1 1K BLU2 510 U7 V7 N7 Pin 5: GND Pin 6: Red GND Pin 7: Grn GND Pin 8: Blu GND Pin 10: Sync GND RED GRN Nexys 4 BLU HSYNC 100 HS N6 VGA signal timings are specified, published, 100 VSYNC copyrighted and sold by the VESA organization VS P7 (www.vesa.org). The following VGA system HD-DB15 Spartan 6 timing information is provided as an example of how a VGA monitor might be driven in 640 by 480 mode. For more precise information, or for information on other VGA frequencies, refer to documentation available at the VESA website. Nexys 3 21 What To Do Friday 1. Show previous lab’s demo 2. Make Verilog module to generate hsync, vsync, horizontal count, vertical count, and signal to indicate active video 3. Use higher-level module to drive RGB using counts gated by active Just do something simple (stripes, checkerboard, diagonals) 4. Later we will use memory addressed by counts to make terminal 22 What do you Need for VGA? Think first Need counter(s)? Will you need a state machine? Sketch out a design Block diagram Test individually in lab Keep in mind Verilog has all these operators (and more; see Verilog ref.) ==, <, >, <=, >= 23 VGA Links VGA Timing Recommended: http://tinyvga.com/vga-timing http://www.epanorama.net/documents/pc/vga_timing.html Interesting http://www.howstuffworks.com/tv.htm http://computer.howstuffworks.com/monitor.htm http://www.howstuffworks.com/lcd.htm http://plc.cwru.edu/ 24