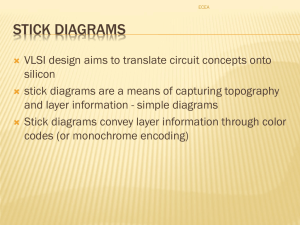

Chapter 4: The Active and Poly Layers

advertisement

Analog VLSI Design Nguyen Cao Qui Introduction to the course • Name: “ Analog VLSI Design ” • Instructor: Nguyen Cao Qui email: ncqui@ctu.edu.vn • Goals: The goal of this course is to introduce the principles of operation, design and technology of Analog Integrated Circuits to Electrical Engineering students at Senior level. VLSI technology and analog integrated circuit design is covered with an emphasis on CMOS Technology. CMOS layout design and analog simulation tools (Cadence) are demonstrated and used. Students will do a design project and final exam at the end. Introduction to the course • Number of credits : 3 (1: theory ; 2: homework + project +Seminar) • Textbooks: “CMOS: Circuit Design, Layout, and Simulation” R. Jacob Baker • Other Books: "CMOS Analog Circuit Design" Phillip E. Allen and Douglas R. Holdberg Introduction to the course • Course Policies: * Homework + Project : 40% * Final Test :60% Conversion 10 ‘ Scale ABCB 0.0 F 4.0 D 4.5 D+ 5.0 C 6.0 C+ 7.0 B 7.8 B+ 8.5 A CONTENTS • • • • • • • • • • • • • • • • Chapter 1: Introduction to CMOS Design Chapter 2: The Well Chapter 3: The Metal Layers Chapter 4: The Active and Poly Layers Chapter 5: CAD Tools (Cadence) Chapter 6: Resistors, Capacitors, MOSFETs Chapter 7: Models for Analog Design Chapter 8: The Inverter Chapter 9: VLSI Layout Examples Chapter 10: Current Mirrors Chapter 11: Amplifiers Chapter 12: Differential Amplifiers Chapter 13: Operational Amplifiers I Chapter 14: Voltage References Chapter 15: Data Converter Fundamentals (ADC) Chapter 16: Data Converter Fundamentals (DAC) Chapter 1 Introduction to CMOS Design • CMOS (complementary metal oxide semiconductor) • CMOS is used in most very large scale integrated (VLSI) or ultra-large scale integrated (ULSI) • "VLSI" : chips containing thousands or millions of MOSFETs. • "ULSI" : containing billions, or more, MOSFETs. • We focus simply on analog CMOS circuit design Introduction to CMOS Design 1. The CMOS IC Design Process The CMOS IC Design Process 1.1 Fabrication • CMOS integrated circuits are fabricated silicon wafers. • Each wafer contains chips or "die" • The most common wafer size is 300 mm 2. CMOS Background • CMOS circuit design was invented in 1963 by Frank Wanlass • Circuit could be made with discrete complementary MOS devices, an NMOS and a PMOS NMOS PMOS 2. CMOS Background * Ex: CMOS Inverter 2. CMOS Background • - Advantages of CMOS: Low power Layout on small area Can be fabricated with few defects and low cost. 95% of ICs are fabricated in CMOS 3. Technology Scale Down * The Moore’s Law : Doubling every 18 months 3. Technology Scale Down Chapter 2: The Well * Studying the well to: • Understanding CMOS integrated circuit layout and design. • Understanding the performance limitations and parasitics. • Understanding the details of each fabrication (layout) layer. Chapter 2: The Well * The Substrate (The Unprocessed Wafer) • CMOS circuits are fabricated on and in a silicon wafer • N-type wafer: doping with donor atoms, exp: phosphorus • P-type wafer: doping with acceptor atoms, exp: boron • P-type wafer: the most common substrate used • NMOS are fabricated directly in the p-type wafer • PMOS are fabricated in an "n-well." Chapter 2: The Well * A Parasitic Diode Chapter 2: The Well * Using the N-well as a Resistor 2.1 Patterning CMOS integrated circuits are formed by patterning different layers on and in the silicon wafer. 2.1 Patterning 2.1 Patterning 2.1.1 Patterning the N-well 2.2 Laying Out the N-well 2.2.1 Design Rules for the N-well 2.3 Resistance Calculation 2.3 Resistance Calculation 2.3 Resistance Calculation * Layout of Corners 2.4. PN Junction Physics Capacitance 2.4. PN Junction Physics Capacitance 2.5. Design Rules for the Well Chapter 3: The Metal Layers • The metal layers: connect circuit elements (MOSFETs, capacitors, and resistors). • There are several metal layers when layout • These levels of metal are named metal1 (M1), metal2 (M2)… 3.1 The Bonding Pad • The interface between the die and the package 3.1.1 Laying Out the Pad Capacitance of Metal-to-Substrate Insulator - Overglass layer 3.2 Design and Layout Using the Metal Layers 3.2.1 Metal1 and Via1 An Example Layout 3.2.2 Parasitics Associated with the Metal Layers Intrinsic Propagation Delay The velocity The delay of the metal line Where 3.2.3 Design Rules for the Metal Layers A Layout Trick for the Metal Layers 3.2.4 Contact Resistance 3.4 Layout Examples 3.4 Layout Examples 3.4 Layout Examples 3.4 Layout Examples 3.4 Layout Examples Chapter 4: The Active and Poly Layers • The active, n-select, p-select, and poly: form n-channel and p-channel MOSFETs. • Metal layers can make an contact to the substrate or well. • The n-select layers indicate where to implant n-type. • The p-select layers indicate where to implant p-type. Chapter 4: The Active and Poly Layers • The active defines an opening in the oxide. • The active and select layers are always used together. • The poly layer forms the gate of the MOSFETs. • Poly is a short name for polysilicon. 4.1 Layout using the Active and Poly Layers • The Active Layer The P- and N-Select Layers The P- and N-Select Layers The Poly Layer • The poly layer is used for MOSFET formation. • The gate of the MOSFET is formed with the polysilicon. • The source and drain of the MOSFET are formed with the n+ implant. Layout and cross-sectional views of a MOSFET. Layout and cross-sectional views of a MOSFET. Layout and cross-sectional views of a MOSFET. The Poly Wire • The poly layer can also be used, as a wire. • Poly is routed on top of the FOX. • The main limitation when using the poly layer for interconnection is its sheet resistance. • The sheet resistance of the metal layers is approximately 0.1 Ohm/square; The poly layer: 200 Q/square. • The delay through a poly line can be considerably longer than a metal line. The Poly Wire 4.1.1 Process Flow 4.1.1 Process Flow 4.2 Connecting Wires to Poly and Active 4.2 Connecting Wires to Poly and Active Connecting the P-Substrate to Ground Layout of an N-Well Resistor Layout of an NMOS Device Layout of a PMOS Device Design Rules Design Rules