DDR Memory Power

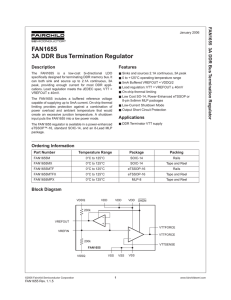

advertisement

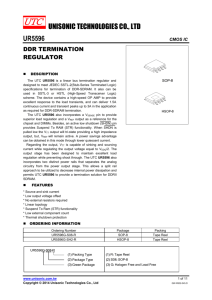

DDR Memory – what is it? Understanding DDR Memory • Double Data Rate Memory – Read/Write on both Rising and Falling Edge • 2x Speed without increasing CLK frequency • Faster Transitions – Low Voltage (2.5V, 1.8V, 1.5V) • Lower Threshold Voltages • Lower noise margin Understanding DDR Memory • Conventional Logic – Fixed Input Threshold – High Impedance Termination – Terminated to I/O Supply I/O Supply Input Stage Output Stage Output Input + Memory Cell + VTH Conventional Memory Block Diagram • Stub Logic (DDR Memory) – ½ VIO Threshold – Low Impedance Termination – Terminated to ½ I/O Supply VDDQ Input Stage VTT Output Stage Rterm Input VTT_REF + Memory Cell DDR Memory Block Diagram Output VDDQ, VTT What does it all mean? • VDDQ – VCC – Memory Core Power – VDD – Memory Logic Power – VI/O – Input/Output Stage Power • 2.5V (DDR), 1.8V (DDR2) or 1.5V (DDR3) • 3% Accuracy, 1.5% ripple, 50mV transient • VTT_Ref – Typically less than 1mA / device – Low Current Logic Threshold Level • ½ VDDQ • 2% Accuracy, <10mV ripple • VTT – High-Current Termination Voltage • VTT_Ref • 20mV Accuracy, 1% ripple, 40mV transient VDDQ, VTT, What does it all mean? • VDDQ – Provides Core,Logic and I/O Power • Typical low voltages – 2.5V on older DDR – 1.8V on current DDR2 – 1.5V on newest DDR3 • Generally Produced with a High-speed switcher – Single Chip can be as low as 1-2 Amps – Use Single Channel Switcher smaller banks (3 – 15A) – Use Multi-Channel Switchers for large, multi-DIMM banks – High Transient requirement can require large output capacitor bank. VDDQ, VTT, What does it all mean? • VTT_ref – Provides Reference for Logic Input-Stage • Must be ½ VDDQ of Source device – Can be generated by Resistor Divider • Typical for up to 4 Chips or 1 DIMM – Generate with active buffer • Less load sensitive – higher accuracy • Higher divider resistance – Less dissipation • Necessary for larger multi-DIMM banks VDDQ, VTT, What does it all mean? • VTT – High-Current Sink/Source Termination • Source Current for Logic 0 • Sink Current for Logic 1 – High Dynamic Currents • -IMAX to +IMAX at 5A/ms not uncommon • 40mV transient response • Typical requires large bulk capacitance – Typically generated with Tracking Switcher OR Sink/Source LDO • Tracking Switchers may require external resistor divider • Standard LDO’s can-not sink current VTT Termination – Passive • Simple Resistor Termination • 90mA Termination • 162mW Dissipation • Inexpensive • Poor Performance • Lower Through Put • Higher Bit-Error VDDQ 1.8V 20 10 VOUT 20 VTT 0.9V 50 10 Passive Termination - Loading VDDQ 1.8V 20 96mA VOUT 20 12mA 2 10 VTT 0.9V VDDQ 1.8V 0.84V! VOUT 50 84mA Write 1 more Zero 10 128mA 2 110mA 10 VTT 0.9V 0.772V! 5 77mA Writing 10 more Zeros 10 How Much Power do I need? • VTT_REF – Low Current Requirement – Typically less than 1mA / device – VTT_REF leakage current typical given in DDR IC or DIMM datasheet How Much Power do I need? • VTT – Typically NOT given in datasheet – Depends on Address & Datalines ITTMAX # bitsVTT R TERM • DDR – Can be as high as 20mA / data/address bit channel • DDR2 – Can be as high as 18mA / data/address bit • DDR3 – Can be as high as 15mA / data/address bit – Can have upto 2x start-up current due to Active Termination / Capacitive Load How Much Power do I need? • VDDQ – In Datasheet • Datasheets list IDDQ for every mode – Not all IC/DIMMS in highest current mode at once • Typical estimate highest IDDQ mode for 1 IC/DIMM + 50% for each additional IC/DIMM • Given in “No Load” condition – Does not include VTT current • Must Source VTT current to output Logic 1s – Increase by VTT current for I/O when Output All 1s. • IDDQMAX = IDDQ(datasheet) + VTTMAX Integrated Memory Example • Micron 2GB Memory IC • 84pin IC • IDDQ(max) = 350mA • ITT(max) = 13.5mA * 34lines = 460mA • 16 data, 14 address, 4 command • VDDQ = 1.8V @ 810mA • VTT = 0.9V @ 460mA