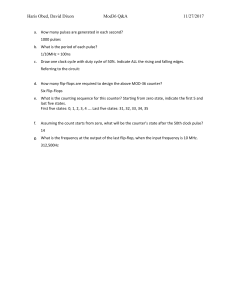

FIRST FEW WORDS TRAFFIC LIGHT This project is done with the acknowledgement of the contribution of document regarding e-traffic light system from falstad simulation; and logic gates, timer IC from Digital Electronics Practice Lab of Electronics and Telecommunications Department in VNUHCM, University of Science. SYSTEM WITH D FLIP-FLOP SHIFT REGISTER MODEL ON FALSTAD SIMULATION 21207001 – Bùi Thành Đạt 21207124 – Nguyễn Thị Trà Chi 21DTV – CLC3 SEPTEMBER 17, 2022 VNUHCM – UNIVERSITY OF SCIENCE Electronics and Telecommunications Department Table of Contents A. Introduction - Observation ............................................................................................................................................. 1 B. Circuit Configuration ....................................................................................................................................................... 1 1. Circuit Overview .......................................................................................................................................................... 1 2. Clock Signal Generator: 555 Timer IC. ........................................................................................................................ 4 3. D flip-flops Shift Register Counter .............................................................................................................................. 1 4. The traffic light system................................................................................................................................................ 5 Reference and Note ................................................................................................................................................................ 7 A. Introduction - Observation Traffic light goes in the sequence of green, yellow, and red as a loop with each light shows up for a pre-determined time. From the first observation, the system can be divided into two parts: the time for the light, and the lights. For the four-way intersection (also known as a cross intersection), the light traffic system on a straight road shares the same state. For example, when the light in the north is green, the light in the south shares that same green. The same thing happens for 4 directions. The time of a red light is the total time of green light and yellow light come from the perpendicular direction. The yellow light has the shortest time as this is a warning signal. The green light must have long enough time for the cars to pass the intersection. From now on, regarding to the north side is the same as the south, as they share the same state. Same procedure happens for the east and the west. B. Circuit Configuration 1. Circuit Overview Circuit Falstad Simulation Link: https://tinyurl.com/2e8zdruw Clock Signal • 555 timer IC: Astable mode. • Enable the counting ability of the counting system. Counting • Use a shift register counter. • Take the idea of ring counter and Johnson counter. • Use combination of D flip-flops and logic gates to produce wanted sequence. Block B.1.1: Block Diagram of the traffic light system. Traffic Light • The system is sequencecontrolled by the counter Image B.1.1: Complete traffic light system using 555 Timer IC and D flip-flop Shift Register Counter. For easier mentioning, the circuit can be divided into 3 main parts highlighted by different colors: the clock signal generator (green zone), the counter (pink zone), and the traffic lights (blue zone). Image B.1.2: Highlighted zone of the circuit. 2. Clock Signal Generator: 555 Timer IC. To have flip-flops working properly, having a clock signal generator is a must since there are only two options in falstad: to use a provided clock signal generator, or to use a 555 Timer IC. There is not much any other choice like CD4060 or else in the program. In this project, the 555 timer is used. Image B.2.1: Schematic Image of 555 Timer IC. The 555 Timer IC has 4 different operating modes: - - Monostable mode: it functions as a "one-shot" pulse generator, producing a precision timer of a fixed time duration. Bistable mode: to produce a SR flip-flop type switching action. Astable mode: to produce a very stable 555 Oscillator circuit for generating highly accurate free running waveforms. o This mode takes the idea of a 555 monostable circuit which stops after a preset time, and continuously re-trigger the 555 IC after each timing cycle. o This re-triggering is achieved by connecting the trigger input (pin 2) and the threshold input (pin 6) together, thereby allowing the device to function as an astable oscillator. o The output frequency can be adjusted by means of an externally connected RC tank circuit consisting of just two resistors and a capacitor. Schmitt trigger (inverter) mode – the 555 operates as a Schmitt trigger inverter gate which converts a noisy input into a clean digital output. In this circuit, the 555 Timer IC is set in “Astable Multivibrator” mode. Image B.2.2: Operation of the 555 Timer IC in the Astable Multivibrator mode. The configuration for the 555 IC: of resistors and capacitor 𝑅𝑅1 = 𝑅𝑅2 = 10𝑘𝑘 𝑜𝑜ℎ𝑚𝑚 𝐶𝐶 = 104 𝜇𝜇𝜇𝜇 The specification of clock signal generated by the IC: 𝑇𝑇𝑜𝑜𝑜𝑜 = 0,693 ∗ (𝑅𝑅1 + 𝑅𝑅2 ) ∗ 𝐶𝐶 = 1,386 𝑚𝑚𝑚𝑚. 𝑇𝑇𝑜𝑜𝑜𝑜𝑜𝑜 = 0,693 ∗ 𝑅𝑅2 ∗ 𝐶𝐶 = 693 𝜇𝜇𝜇𝜇. 𝑇𝑇 = 𝑇𝑇𝑜𝑜𝑜𝑜 + 𝑇𝑇𝑜𝑜𝑜𝑜𝑜𝑜 = 2,079 𝑚𝑚𝑚𝑚. 𝑓𝑓 = 𝐷𝐷𝐷𝐷𝐷𝐷𝐷𝐷 𝑐𝑐𝑐𝑐𝑐𝑐𝑐𝑐𝑐𝑐 = 1 = 481 𝐻𝐻𝐻𝐻 𝑇𝑇 𝑅𝑅1 + 𝑅𝑅2 = 0.66 = 66% 𝑅𝑅1 + 2𝑅𝑅2 Image B.2.3: The configuration of 555 Timer IC in the circuit. 3. D flip-flops Shift Register Counter The timing countdown for the traffic lights can simply use a counter system. There are a wide range of choices to create a counter that not only works perfectly well with the system, but also takes minimal effort for easy time modification in the future. It can be a cascaded JK flip-flops, or simply a ring counter that use an 𝑂𝑂𝑂𝑂 logic gate, and so on… (in the ring counter configuration, the number of input that is connected to the 𝑂𝑂𝑂𝑂 logic gate which taken from the counter outputs, is equals the time that the output light shows up). Image B.3.1: An example using ring counter taken from falstad e-traffic example. It is possible to use other types such as cascaded JK flip-flops or to use a ring counter, which are both much easier to setup and to observe when compared to using D flip-flops Shift Register Counter. However, the highest advantage of D flip-flop is that its state transition table is very minimal. However, there are some certain advantages when using a D flip-flop system as a counter for this particular circuit. Take those into comparison: JK flip-flop: - - Most of the time, there must be a full process to create a counter (or a state machine) due to the complexity of JK preset inputs. The process to create the preset for the inputs of JK flip-flops: o State Diagram. o Next-state Table. o Flip-flop Transition Table. o Karnaugh Map. o Logic Expressions for Flip-flop Inputs. o Counter Implementation. However, that process is must needed when trying to produce the same result that is used in the D flip-flops Shift Register Counter in this project. D flip-flop: - The Q output is the same as the D input at the time it receives a clock pulse. As it has this advantage, the process can be simplified by connecting flip-flops as a shift register, then sequentially placing logic gates that set or reset the flip-flops based on the need of the design. In this project, D flip-flops Shift Register Counter was chosen particularly for educational research purpose. Thanks to the simple output transition design of D flip-flops, designing the counter was not much of a racking brain task. That means tools helping to create cascaded counter like next-state table, transition table and Karnaugh map were unneeded when implementing the circuit. Those tools were only used in this project specifically for final analysis and verification of the circuit. Image B.3.2: Flip-flop part of the circuit. To make it easier, the illustration has different zones highlighted, and the flip-flops are numbered. Image B.3.3: Highlighted zone and numbered flip-flops. From now on in this D flip-flops Shift Register Counter part, each of these colors responsible for zones/signal: Green: Green light A. Yellow: Yellow light A. Blue: Green light B. Pink: Yellow light B. A is for mentioning North and South, while B is for West and East. Let us call A and B are 2 different traffic light control system which have opposite state when compared to the other one (or it can also understand to be in a perpendicular position when compared to the other). - 𝑅𝑅𝐴𝐴 : Red light A, 𝑅𝑅𝐵𝐵 : Red light B. 𝑌𝑌𝐴𝐴 : Yellow light A, 𝑌𝑌𝐵𝐵 : Yellow light B. 𝐺𝐺𝐴𝐴 : Green light A, 𝐺𝐺𝐵𝐵 : Green light B. To simplify the implementation of different lights, an 𝑂𝑂𝑂𝑂 logic gate was used to add both the time of the yellow light and the green light which come from the perpendicular direction, outputting red light’s time. 𝑇𝑇𝑅𝑅𝐴𝐴 = 𝑇𝑇𝑌𝑌𝐵𝐵 + 𝑇𝑇𝐺𝐺𝐵𝐵 𝑇𝑇𝑅𝑅𝐵𝐵 = 𝑇𝑇𝑌𝑌𝐴𝐴 + 𝑇𝑇𝐺𝐺𝐴𝐴 That also means there is no need to consider the red lights anymore, as red lights’ time is the total time of yellow light and green light comes from perpendicular direction. These outputs of the flip-flops account for the input of the lights: 𝐺𝐺𝐴𝐴 = 𝑄𝑄0 𝑌𝑌𝐴𝐴 = 𝑄𝑄3 𝐺𝐺𝐵𝐵 = 𝑄𝑄5 The expression for the inputs of D flip-flop: 𝑌𝑌𝐵𝐵 = 𝑄𝑄6 𝐷𝐷0 = 𝑄𝑄2 𝑄𝑄5 𝐷𝐷1 = 𝑄𝑄0 𝐷𝐷2 = 𝑄𝑄1 𝐷𝐷3 = 𝑄𝑄0 𝑄𝑄2 𝑄𝑄3 𝐷𝐷4 = 𝑄𝑄2 𝐷𝐷5 = 𝑄𝑄4 𝐷𝐷6 = 𝑄𝑄4 𝑄𝑄5 Clock Pulse Present-state Table 𝑸𝑸𝟑𝟑 0 𝑸𝑸𝟎𝟎 𝑸𝑸𝟏𝟏 𝑸𝑸𝟐𝟐 0 0 0 0 1 1 2 1 1 3 1 1 1 4 1 1 5 1 6 7 8 9 1 10 1 1 11 1 1 1 12 1 1 13 1 14 15 16 *The blank blocks in the table means that it is in the state 0. 𝑸𝑸𝟒𝟒 0 1 1 1 1 𝑸𝑸𝟔𝟔 0 1 1 1 1 1 1 1 1 1 1 1 1 Table B.3.1: Present-state of the D flip-flop Shift Register Counter. 1000000 •Start from 0000000 0000001 1100000 0000010 1110000 0010110 𝑸𝑸𝟓𝟓 0 0111000 Diagram B.3.2: State Diagram of the D flip-flop Shift Register Counter. 4. The traffic light system Image B.4.1: Traffic light system. Traffic lights on the same direction are wired together as they share the same light state. All the lights are connected to a 220 𝑜𝑜ℎ𝑚𝑚 resistor, then to the ground. The red light is combined of the green light and yellow light. 𝑇𝑇𝑅𝑅𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ = 𝑇𝑇𝑌𝑌𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 + 𝑇𝑇𝐺𝐺𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 𝑇𝑇𝑅𝑅𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 = 𝑇𝑇𝑌𝑌𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ + 𝑇𝑇𝐺𝐺𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ From that, the combination that the red light receive is by using the 𝑂𝑂𝑂𝑂 logic gate. 𝑅𝑅𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ = 𝑌𝑌𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 + 𝐺𝐺𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 𝑅𝑅𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 = 𝑌𝑌𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ + 𝐺𝐺𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ The lights are connected to the output of flip-flops: 𝐺𝐺𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ = 𝑄𝑄0 𝑌𝑌𝑁𝑁𝑁𝑁𝑁𝑁𝑁𝑁ℎ/𝑆𝑆𝑆𝑆𝑆𝑆𝑆𝑆ℎ = 𝑄𝑄3 𝐺𝐺𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 = 𝑄𝑄5 𝑌𝑌𝑊𝑊𝑊𝑊𝑊𝑊𝑊𝑊/𝐸𝐸𝐸𝐸𝐸𝐸𝐸𝐸 = 𝑄𝑄6 Reference and Note https://unsplash.com/photos/UH0vzjrG78M Image B.2.1: https://www.build-electronic-circuits.com/555-timer/ Image B.2.2: Figure 7 – 57; Floyd, Thomas L. Digital fundamentals / Thomas L. Floyd.—Eleventh edition. pages cm ISBN 978-0-13-273796-8 (0-13-273796-5) 1. Digital electronics. 2. Logic circuits. I. Title. TK7868.D5F53 2015 621.381—dc23 Idea and image B.3.1: https://www.falstad.com/circuit/e-traffic.html https://www.electronics-tutorials.ws/waveforms/555_oscillator.html All the lectures in 2022 from Digital Electronics Practice Lab – VNUHCM, University of Science