CMOS Inverter Power Dissipation: Dynamic, Short Circuit, Leakage

advertisement

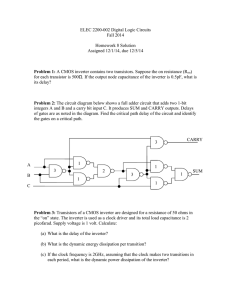

Power Dissipation © Digital Integrated Circuits2nd Inverter Where Does Power Go in CMOS? • Dynamic Power Consumption Charging and Discharging Capacitors • Short Circuit Currents Short Circuit Path between Supply Rails during Switching • Leakage Leaking diodes and transistors © Digital Integrated Circuits2nd Inverter Dynamic Power Dissipation Vdd Vin Vout CL Energy/transition = CL * Vdd2 Power = Energy/transition * f = CL * Vdd2 * f Not a function of transistor sizes! Need to reduce CL, Vdd, and f to reduce power. © Digital Integrated Circuits2nd Inverter (c) Assume sizing S1, S2 and S3 to be 1 What is the total energy consumed for a full cycle (0→ VDD, VDD→ 0)? Solution: The total capacitance charged during a full cycle (0→ VDD, VDD→ 0) is: Ctotal C C C C C C C 256C 263C Etotal © Digital Integrated Circuits2nd 263CV D 2 Inverter Short circuit Power Dissipation © Digital Integrated Circuits2nd Inverter Short circuit power observations Consider a static CMOS inverter with a 0 ->1 transition at the input. Assume first that the load capacitance is very large, so that the output fall time is significantly larger than the input rise time. Under those circumstances Input moves through the transient region before the output starts to change. As the source-drain voltage of the PMOS device is approximately 0 during that period, the device shuts off without ever delivering any current. The short-circuit current is close to zero in this case. Consider now the reverse case, where the output capacitance is very small, and the output fall time is substantially smaller than the input rise time . The drain-source voltage of the PMOS device equals VDD for most of the transition period, guaranteeing the maximal short-circuit current (equal to the saturation current of the PMOS). © Digital Integrated Circuits2nd Inverter Short Circuit Currents © Digital Integrated Circuits2nd Inverter Minimizing Short circuit power Peak current determined by MOSFET saturation current, so directly proportional to device sizes Peak current also strong function of ratio between input and output slopes as shown in previous slide For individual gate, minimize short circuit current by making output rise/fall time much bigger than input rise/fall time Slows down circuit Increases short circuit current in fanout gates Compromise: match input and output rise/fall times © Digital Integrated Circuits2nd Inverter Minimizing Short-Circuit Power 8 7 6 Vdd =3.3 Pnorm 5 4 Vdd =2.5 3 2 1 Vdd =1.5 0 0 1 2 3 4 5 t /t sin sout © Digital Integrated Circuits2nd Inverter Leakage Vd d Vout Drain Junction Leakage Sub-Threshold Current Sub-threshold current one of most compelling issues Sub-Threshold Dominant Factor in low-energy circuitCurrent design! © Digital Integrated Circuits2nd Inverter © Digital Integrated Circuits2nd Inverter