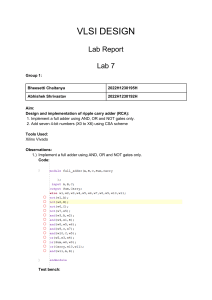

SYNOPSIS OF PROPOSED THESIS ON Design and Analysis of 1-bit Full Adder in CMOS 45nm Technology Submitted to the Dean, Post Graduate Studies G. B. Pant University of Agriculture and Technology Pantnagar-263145, U.S. Nagar, Uttarakhand By Km Shweta Bhandari (Id. No-59586) M. Tech (Electronics and communication Engineering) Under the guidance of Dr. Abhishek Tomar Professor Department of Electronics and Communication College of Technology Govind Ballabh Pant University of Agriculture and Technology Pant Nagar – 263145 (U.S. Nagar), Uttarakhand, INDIA SYNOPSIS Name : Km Shweta Bhandari ID No. : 59586 Degree Programs : M. Tech (Electronics and communication engineering) Major : Electronics and communication engineering Advisor : Dr. Abhishek Tomar Department of Electronics and communication engineering Tentative Title : Design and Analysis of 1-bit Full Adder in CMOS 45nm Technology It is certified that the above synopsis has been thoroughly examined and found suitableby the following members of the advisory committee CHAIRMAN AND MEMBERS OF THE ADVISORY COMMITTEE (Dr. Abhishek Tomar) Professor Chairman Advisory Committee Department of Electronics and Communication Engineering (Dr. Paras) Professor Dept. of ECE (Member) Head Dept. of ECE (Dr. Reeta Verma) Associate Professor Dept. of ECE (Member) Dean College of Technology Mr. Sanjay Joshi Assistant Professor Dept. of IT (Member) Dean PGS INTRODUCTION The first integrated circuit (IC) was invented in 1958, since then the foremost concern of the circuit designers was to speed up the digital design and to decrease the area. Subsequently, the manufacturing of a complete system on a single chip (SOC) has been possible with advancement in Very Large-Scale Integration (VLSI) fabrication technology, which has also facilitated the improvement of cellular phones, laptops, handheld computers, and mobile multimedia systems (capable of real-time speech recognition and real-time video display) (Darwish and Bayoumi, 2004). During the last few years, the increase in the chip density has led to an increase in the power consumption. Hence, power consumption is also one of an important parameter in digital design as speed and area. To decide the performance, the high chip density is one of the critical components. Moore law predicts that the chip density, which defines the number of transistors fabricated in one chip, increases by 1.5 times every year (Moore, 1965). A recent analysis done by combining Moore’s law and other particle limits projected that 100 G transistor chip will be available by 2020 (Gelsinger, 2004; Schaller, 1997) Through rigorous analysis and simulation using industry-standard tools, the performance metrics of the CMOSbased 1-bit full adder are evaluated. Parameters such as propagation delay, power consumption, and noise margins are investigated to ensure the circuit meets the requirements of modern digital systems. Furthermore, the paper explores techniques for optimizing the full adder design, including transistor sizing, layout optimization, and gate-level modifications, aiming to enhance performance metrics while maintaining area efficiency and manufacturability. The experimental results demonstrate the effectiveness of the proposed CMOS-based 1-bit full adder in terms of speed, power efficiency, and robustness against noise. The findings contribute to advancement of digital circuit design methodologies, providing insights into the practical implementation of highperformance arithmetic circuits using CMOS technology. Overall, this research underscores the significance of CMOS-based 1-bit full adders in the development of efficient and reliable digital systems, offering valuable insights for future advancements in integrated circuit design and fabrication technology. Complementary Metal-Oxide-Semiconductor (CMOS) logic is widely used in integrated circuits, microprocessors, microcontrollers, and various digital logic circuits. It is known for its ability to reduce power consumption and its resilience to noise. CMOS logic employs complementary and symmetrical pairs of transistors, including P-type Metal-Oxide-Semiconductor Field-Effect Transistors (PMOS) and N-type Metal-Oxide-Semiconductor Field-Effect Transistors (NMOS), to implement logic functions efficiently. 1.1 Advantages of CMOS: Low Power Consumption: CMOS circuits consume less power compared to other logic families, making them ideal for battery-operated devices and energy-efficient systems. High Noise Immunity: CMOS circuits are less susceptible to noise interference, ensuring reliable operation in noisy environments. Design Flexibility: CMOS technology allows for complex logic designs and integration of multiple functions on a single chip. Functionality: CMOS logic supports a wide range of logic functions, making it versatile for various applications in digital systems. 1.2 Disadvantages of CMOS: High Input Capacitance: CMOS gates exhibit high input capacitance, which can reduce the overall performance of the circuit, particularly in terms of speed. Complexity: While CMOS offers design flexibility, complex circuits may require more transistors and layout considerations, leading to increased complexity in the design process. 1.3 Full Adder: A full adder is a crucial component in digital circuits used for arithmetic operations. It adds three input bits (A, B, and Carry-in) to produce two outputs: Sum (SUM) and Carry-out (Cout). The full adder comprises two half adders and additional logic for handling the carry input. 1.3.1 Conventional Full Adder: The conventional full adder typically employs a larger number of transistors, such as 28T or more, to implement the logic functions effectively. Despite its complexity, the conventional full adder ensures accurate arithmetic computations and is commonly used in various digital systems. In summary, CMOS logic offers significant advantages in terms of power efficiency, noise immunity, and design flexibility. The full adder, whether conventional or implemented with fewer transistors, plays a crucial role in digital arithmetic circuits, facilitating accurate computations and reducing power consumption. A 1-bit full adder is a fundamental digital circuit used in computer arithmetic to add two binary numbers. It takes in three inputs: two bits to be added (A and B) and a carry input (Cin) from a previous stage if the full adder is part of a multi-bit adder. The output consists of a sum bit (S) and a carry-out bit (Cout). Here's a breakdown of its operation: Inputs: A: One of the binary digits to be added. B: The other binary digit to be added. Cin: The carry input from a previous stage if part of a multi-bit adder. Outputs: S: Sum output, which is the XOR of A, B, and Cin. Cout: Carry-out, which is generated when at least two inputs (A, B, or Cin) are high. Truth Table: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 The logic for the sum (S) can be represented as: S = A’BCin+AB’Cin+ABCin’+ABCin The carry-out (Cout) can be expressed as: Cout =A⋅B+(A+B). Cin Sum 0 1 1 0 1 0 0 1 Carry 0 0 0 1 0 1 1 1 Fig no.1- basic full adder circuit using gate 1.4 CMOS Technology: Complementary metal-oxide semiconductor (CMOS) logic is used in integrated circuit microprocessors, microcontrollers and other digital logic circuits to reduce power consumption and being more immune to noise occurring conditions. In the CMOS there are complementary and Symmetrical pairs which are of P-type (PMOS) and N-Type (NMOS) which are used for implementation of logic functions. In a PMOS transistor we can have input from voltage source or from other PMOS transistor. NMOS transistor can have input from ground or other NMOS transistor. Low power, high noise margin, design ease, functionality are the main advantages of CMOS and high input capacitance reduces the ultimate performance are the disadvantages. These days close-packed, high performance, efficient, low power microprocessors are in demand. The central processing unit (CPU) is an integral part of each microprocessor. Key element of CPU is Arithmetic Logic Unit. ALU can perform basic arithmetic and logical operations. Addition is the most used arithmetic operation in microelectronic systems, and it is one of the speed-limiting elements. There are various full adder designs that have been designed owing to its significance in many micro-electronic circuits. The full adder circuit is the core of many digital and analog circuits. Therefore, the development of the adder in terms of efficient parameters such as speed and power consumption should be pursued. It is necessary to optimize the performance of full adder cells for fast and low energy operations of arithmetic blocks. So, energy efficient, high speed, low power and reliable microprocessors are in demand in the recent and innovative silicon technology processes have resulted in the rapid growth of modern IC. Various performance determining Factors are strongly influenced by chosen logic style. So, the objective of the paper is to find the most efficient logic style between CMOS and Transmission Gate for 1- bit Full Adder circuit. 1.4.1 Parameters of PMOS and NMOS: Parameters PMOS NMOS Low resistance Low gate voltage High gate voltage High resistance Low gate voltage Low gate voltage Fig no.2: Conventional CMOS full adder circuit Complementary MOS Logic Style (CMOS) D Complementary MOS Logic Style consists of Pull-Up Network (PUN), which has PMOS transistors and the Pull-Down Network (PDN), which consists of NMOS transistors. The Pull-Up Network connects the output of the gate with Vdd whenever the output of the gate is high. The Pull-Down Network connects gate output and GND when the gate output is low. This logic style consists of 28 transistors. REVIEWS OF LITERATURE A 1-bit full adder is a fundamental building block in digital circuit design, crucial for arithmetic operations in processors, calculators, and various other computational systems. With the continuous advancement of integrated circuit technology, designers are constantly exploring novel approaches to enhance performance, reduce power consumption, and improve the reliability of 1-bit full adders. This literature review delves into recent developments and research efforts focused on designing and optimizing 1-bit full adders using Complementary Metal-Oxide-Semiconductor (CMOS) technology. CMOS technology is widely utilized in modern digital circuits due to its low power consumption, high integration density, and compatibility with scaled-down fabrication processes. The primary objective of this review is to provide an overview of the state-of-the-art techniques, methodologies, and design considerations employed in the development of 1-bit full adders. It encompasses studies published in peer-reviewed journals, conference proceedings, and research papers that address key aspects such as speed, power efficiency, area utilization, and robustness. By examining a range of literature sources, this review aims to identify trends, challenges, and opportunities in the field of 1-bit full adder design using CMOS technology. The insights gained from this review are valuable for both academic researchers and industry practitioners involved in digital circuit design and optimization. Overall, this literature review serves as a comprehensive guide to understanding the current landscape of 1-bit full adder design methodologies in CMOS technology, paving the way for future advancements in digital arithmetic circuits. D. Radhakrishnan (2001) realized a hybrid 1-bit FA using PTL with 14-transistors. This design improved the performance of the adder cell to remove the inverter in the critical path and also eliminates the short circuit power component. To check the testability of this design HSPICE simulator is used with 0.35μm CMOS technology. This design gave 4% improvement in delay and has a good noise margin due to full swing at the internal nodes. Hung Tien Bui et al. (2002) presents a detailed design and implementation of a 1-bit full adder using CMOS technology. The authors explore various CMOS logic styles and compare their performance in terms of speed, power consumption, and area utilization. In this paper two different 1-bit CMOS full adder logic design styles have been implemented, simulated, analyses and compared. This together with its significant delay reduction makes it the circuit of choice for low-power, low-voltage and highperformance implementation, like multipliers Mingyan Zhang et al. (2003) is proposed for a new low power and high-performance adder cell using a new design style called "Bridge” is proposed. The bridge design style enjoys a high degree of regularity, higher density than conventional CMOS design style as well as lower power consumption, by using some transistors, named bridge transistors. Simulation results illustrate the superiority of the resulting proposed adder against conventional CMOS 1-bit full-adder in terms of power, delay and PDP. We have performed simulations using HSPICE in a 90 nanometer (nm) standard CMOS technology at room temperature; with supply voltage variation from 0.65v to 1.5v with 0.05v step. C.H. Chang et al. (2005) realized 1-bit full adder designs implemented in CMOS technology. It evaluates these designs based on parameters like power dissipation, delay, and area, providing insights into the trade-offs involved in designing efficient full adders. The 1-bit full adder circuit is one of the most used extensively in many very large-scale integration circuits such as application- specific digital signal processing systems and microprocessors. An advert is used for the overall analysis of the circuits in most of the systems. This paper describes various types of full adders based on different techniques for low power. All the analysis depends on some different simulation parameters such as transistor count, delay, power-delay product, power consumption, and the value of power supply. Each full adder used a different tool for the simulation purpose. M. Alioto et al. (2007) analyze the performance of various 1-bit full adder cells in CMOS technology, considering factors such as process variations and environmental conditions. They propose techniques to enhance robustness and reliability in full adder designs. A performance analysis of 1-bit full-adder cell is presented. The adder cell is anatomized into smaller modules. The modules are studied and evaluated extensively. Several designs of each of them are developed, prototyped, simulated and analyzed. Twenty different 1-bit full-adder cells are constructed (most of them are novel circuits) by connecting combinations of different designs of these modules. Each of these cells exhibits different power consumption, speed, area, and driving capability figures. Two realistic circuit structures that include adder cells are used for simulation. A library of full-adder cells is developed and presented to the circuit designers to pick the full-adder cell that satisfies their specific applications. O. Kavehei et al. (2008) introduces a novel design approach for a 1-bit full adder optimized for low power applications. The authors discuss circuit-level optimizations and layout strategies to minimize power consumption while meeting performance requirements. A novel design of a hybrid Full Adder (FA) using Pass Transistors (PTs), Transmission Gates (TGs) and Conventional Complementary Metal Oxide Semiconductor (CCMOS) logic is presented. Performance analysis of the circuit has been conducted using Cadence toolset. For comparative analysis, the performance parameters have been compared with twenty existing FA circuits. The proposed FA has also been extended up to a word length of 64 bits in order to test its scalability. Only the proposed FA and five of the existing designs have the ability to operate without utilizing buffer in intermediate stages while extended to 64 bits. K. Navi et al. (2009) introduce low-power full-adder based on CMOS inverter is presented. This full adder is comprised of inverters. Universal gates such as NOR, NAND and MAJORITY-NOT gates are implemented with a set of inverters and non-conventional implementation of them. In the proposed design approach, the time consuming XOR gates are eliminated. As full-adders are frequently employed in a tree-structured configuration for high-performance arithmetic circuits, a cascaded simulation structure is employed to evaluate the full-adders in a realistic application environment. The circuits being studied were optimized for energy efficiency using 0.18 μ m and 90 nm CMOS process technologies. The proposed full adder shows full swing logic, balanced outputs and strong output drivability. It is also observed that the presented design can be utilized in many cases especially whenever the lowest possible power consumption is targeted. M. Aguirre-Hernandez et al. (2011) present two high-speed and low-power full-adder cells designed with an alternative internal logic structure and pass-transistor logic styles that lead to have a reduced power-delay product (PDP). We carried out a comparison against other full adders reported as having a low PDP, in terms of speed, power consumption and area. All the full-adders were designed with a 0.18μm CMOS technology and were tested using a comprehensive testbench that allowed to measure the current taken from the full-adder inputs, besides the current provided from the power-supply. Post-layout simulations show that the proposed full adders outperform its counterparts exhibiting an average PDP advantage of 80%, with only 40% of relative area. Manjunath K M et al. (2015) adder is an important part in any processor/controller design. To date there are plenty of 1-bit full-adder circuits which have been proposed and designed. In this paper we have an analytic and comparative description of various full adder circuits, considering various constraints like power consumption, speed of operation and area. The circuits are designed in the virtuoso platform, using cadence tool with the available GPDK - 45nm kit. The Full adder circuits with the most 28 transistors to the one with only 6 transistors are successfully designed, simulated and compared for various parameters like power consumption, speed of operation(delay) and area (transistor count), and finally concluded the best designs, that suite for the specifications. Bhattacharyya et al. (2014) realized a hybrid FA with different design modules using 16-transistors. Module I was used as an inverter to generate the XNOR signal from the XOR signal. Module II and Module III were implemented using the TG and MUX, respectively. This FA design was found to have the fastest among previous circuits of FA and have lesser delay and smaller number of transistors. All the simulations were done in the Cadence Virtuoso tool with 180/90nm CMOS process technology. By applying the 1.8V supply voltage at 180nm technology, this design gave 30 to 79 % and 20 to 82 % improvement in power consumption and PDP, respectively. Besides, at 1.2 V of supply voltage with 90nm technology, this design gives 24 to 82 % and 84 to 92 % improvement in power consumption and PDP, respectively. Vijayakumar (2021) multiplier plays an important role in the design of FIR filters in digital signal processors (DSP). In VLSI the multipliers performance speed affects the overall speed of the system. Moreover, multiplication process uses execution time in most of the DSP devices. Hence, high speed is required in multipliers. This paper presents the analysis of a high-speed new radix-4 multiplier using Shannon adder. The proposed hybrid adder is implemented to achieve higher reduction of power in the high-speed parallel radix-4 multiplier. Hence this modified radix-4 multiplier is a suitable candidate for obtaining less propagation delay, low power consumption and better power delay product. The circuit simulations are done using Synopsys H-Spice software. The obtained simulation results exhibit that the proposed structure performance is better in terms of Propagation delay, low power consumption and Power delay product when compared with the advanced technology in CMOS. Kanojia (2022) introduce an intensive demand for energy-efficient computing gadgets. To optimize the arithmetic unit of these devices, this paper presents a 1-bit full adder cell designed using a hybrid logic scheme. The reported cell employs 18-transistors and performs better than existing hybrid full adder cells, while maintaining full swing output and minimum chip-area. The layout design simulation is performed on 65 nm, 45 nm and 32 nm technology nodes. The power consumption, delay and power-delay product are reduced by 20%, 36.45% and 40.13%, respectively as compared to the earlier reported hybrid full adder circuits. In addition, the layout area is improved up to 41.32%. The improved performance of the proposed hybrid full adder cell is validated at different voltages and temperatures. MATERIALS AND METHODS The materials and methods used in designing a 1-bit full adder depend on the specific technology and design approach chosen. Here's a general outline of materials and methods commonly used in CMOSbased 1-bit full adder design: 3.1 Materials: CMOS Transistors: Complementary Metal-Oxide-Semiconductor (CMOS) technology is the foundation for building digital circuits. It utilizes both NMOS (n-channel MOS) and PMOS (pchannel MOS) transistors to implement logic functions. Substrates: Silicon is the most common substrate material used in CMOS technology due to its semiconductor properties. Interconnects: Metal layers are used for interconnects to connect transistors and form circuit paths. Dielectric Layers: Insulating dielectric layers (e.g., silicon dioxide) are used between metal layers to prevent short circuits and provide isolation. Using Cadence Virtuoso 45nm technology in the design of a 1-bit full adder involves several steps within the software environment. Here's an outline of how Cadence Virtuoso can be utilized in the design process. 3.2 Methods: Logic design: The first step is to design the logic functionality of the 1-bit full adder using Boolean expressions or truth tables. This involves determining how inputs (A, B, Cin) are combined to produce outputs (Sum, Cout). Schematic Design: Once the logic design is finalized, a schematic diagram is created using Electronic Design Automation (EDA) tools. The schematic represents the circuit's structure, including transistors, interconnects, and power supplies. Layout Design: The schematic is then converted into a physical layout. This involves placing transistors and interconnects according to design rules to ensure proper functionality and manufacturability. Simulation: The designed circuit is simulated using SPICE (Simulation Program with Integrated Circuit Emphasis) or other circuit simulation tools. Simulation helps verify the functionality, performance, and reliability of the full adder design. Fabrication: Once the design is thoroughly validated through simulations, it can be sent for fabrication. Fabrication involves processes such as photolithography, doping, etching, and metal deposition to create the physical CMOS circuit on a silicon wafer. Testing and Characterization: After fabrication, the fabricated chips undergo testing and characterization to ensure they meet specifications. This includes electrical testing, timing analysis, power consumption measurement, and reliability testing. Optimization: Throughout the design process, various optimization techniques may be employed to improve performance metrics such as speed, power efficiency, area utilization, and noise immunity. These methods are fundamental in the design and fabrication of CMOS-based 1-bit full adders, ensuring that the final circuit meets design requirements and performs reliably in digital systems. Software Use: Cadence virtuoso 45 nm technology. Here's an outline of how Cadence Virtuoso can be utilized in the design process: 3.3 Schematic Design: Create Schematic: Launch Cadence Virtuoso and create a new schematic design for the 1-bit full adder. Add Components: Place the necessary components such as CMOS transistors (NMOS, PMOS), resistors, capacitors, and power supplies onto the schematic canvas. Connect Components: Wire the components according to the logic design of the full adder, including input pins (A, B, Cin), output pins (Sum, Cout), and internal logic gates. 3.4 Simulation Setup: Model Selection: Choose appropriate transistor models (e.g., BSIM for MOSFETs) for simulation. Simulation Options: Define simulation options such as transient analysis for dynamic behaviour, DC analysis for biasing, and AC analysis for frequency response. Test bench Creation: Create a testbench to apply input waveforms and simulate the response of the full adder circuit. 3.5 Simulation and Analysis: Simulations: Execute simulations within Cadence Virtuoso to analyze the behavior of the 1-bit full adder under different input conditions. Waveform Viewing: View simulation waveforms to observe outputs (Sum, Cout) in response to input combinations (A, B, Cin). Performance Analysis: Analyze performance metrics such as propagation delay, power consumption, and signal integrity. 3.6 Layout Design: Open Layout Environment: Switch to the layout design environment in Cadence Virtuoso. Create Layout Cells: Create layout cells for each component (transistors, interconnects) based on the schematic design. Place and Route: Place the layout cells on the layout canvas and route interconnects following design rules and constraints. Design Rule Check (DRC): Perform DRC to ensure the layout adheres to manufacturing constraints and rules. By following these steps within Cadence Virtuoso, designers can efficiently design, simulate, and validate a 1-bit full adder using CMOS technology before moving to the fabrication stage. The proposed full adder design contains 3 modules, as you can clearly see in fig no.3. Each module has its own advantages, so we cascaded these modules in such a manner that they work as a standard full adder. Each module is designed in such a way that the complete adder circuit is optimized in terms of the delay, power, PDP, and the layout area. These modules are discussed below in detail. A. We use the 6T XOR/XNOR circuit. This circuit contains six MOSFET’s (P1, P2, P3, N1, N2, and N3). This circuit is based on the cross-coupled p-MOSFET structure and a complementary crosscoupled n -MOSFET structure to produce complement. This circuit provides output for all possible combinations of inputs. The main advantage of this circuit is it has feedback loops that eliminate the threshold voltage loss. For the A = B = 0 and A= B = 1, respectively, these structures do not provide a good output; this is instead provided by the feedback. The XOR signal is generating at the gate terminal of P1, and the XNOR signal is generating at the gate terminal of N1. B. Pass transistor logic (PTL) circuit for generating Sum signal (Module – II) Module II of the proposed design contains two pass transistors. It has been depicted from, the portion of the circuit that is highlighted as Module II has one p MOSFET (P4) and an n MOSFET (N4). In passtransistor logic circuit, the input signals are applied to the gates of the MOSFETs, which act as switches to pass or to block the signal at the output. The MOSFETs are connected in such a way that allows them to function as pass gates, which means they can either allow the signal to pass through or block it. The output signal is obtained from the drain of the MOSFETs and is either the complement or the same as the input signal, depending on the circuit configuration. Here the previous carry (Cin) signal is provided at the gate terminals of P4 and N4. Both the transistors perform AND operations and then OR operations. C. In module III of the proposed circuit, two transmission gate units (the first one contains P5 and N5 MOSFET’s and the second one contains P6 and N6) are used to generate the carry (Cout) signal. In the scaling of various full-adder circuits, voltage degradation is a major problem, and this problem can be resolved by the transmission gate logic. LITERATURES CITED Aguirre-Hernandez, M., & Linares-Aranda, M. 2010. CMOS full-adders for energy-efficient arithmetic applications. IEEE Trans. Very Large Scale Integr. Syst., 19(4): 718-721. Alioto, M., Di Cataldo, G., & Palumbo, G. 2007. Mixed full adder topologies for high-performance low-power arithmetic circuits. Microelectron. J., 38(1): 130-139. Amini-Valashani, M., Ayat, M., & Mirzakuchaki, S. 2018. Design and analysis of a novel low-power and energy-efficient 18T hybrid full adder. Microelectron. J., 74(1): 49-59. Bhattacharyya, P., Kundu, B., Ghosh, S., Kumar, V., & Dandapat, A. 2014. Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 23(10): 2001-2008. Bui, H. T., Wang, Y., & Jiang, Y. 2002. Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 49(1): 25-30. Chandrakasan, A. P., Sheng, S., & Brodersen, R. W. 1992. Low-power CMOS digital design. IEICE Trans. Electron., 75(4): 371-382. Chang, C. H., Gu, J., & Zhang, M. 2005. A review of full adder performances for tree structured arithmetic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 13(6): 686-695. Kandpal, J., Tomar, A., Agarwal, M., & Sharma, K. K. 2020. High-speed hybrid-logic full adder using high-performance 10-T XOR–XNOR cell. IEEE Trans. Very Large Scale Integr. Syst., 28(6): 1413-1422. Kanojia, A., Agrawal, S., & Lorenzo, R. 2023. Comprehensive Analysis of a Power-Efficient 1-Bit Hybrid Full Adder Cell. Wirel. Pers. Commun., 129(2), 1097-1111. Kavehei, O., Azghadi, M. R., Navi, K., & Mirbaha, A. P. 2008. April. Design of robust and highperformance 1-bit CMOS Full Adder for nanometre design. IEEE Comput. Soc. Annu. Symp. VLSI., 48(5): 10-15. Moaiyeri, M. H., Mirzaee, R. F., & Navi, K. 2009. Two New Low-Power and High-Performance Full Adders. J. Comput., 4(2): 119-126. Naseri, H., & Timarchi, S. 2018. Low-power and fast full adder by exploring new XOR and XNOR gates. IEEE Trans. Very Large Scale Integr. Syst., 26(8): 1481-1493. Navi, K., Foroutan, V., Azghadi, M. R., Maeen, M., Ebrahimpour, M., Kaveh, M., & Kavehei, O. 2009. A novel low-power full-adder cell with new technique in designing logical gates based on static CMOS inverter. Microelectron. J., 40(10): 1441-1448. Radhakrishnan, D. 2001. Low-voltage low-power CMOS full adder. IEE Proc.-Circuits Devices Syst., 148(1): 19-24. Tung, C. K., Hung, Y. C., Shieh, S. H., & Huang, G. S. 2007. A low-power high-speed hybrid CMOS full adder for embedded system. IEEE Des. Diagn. Electron. Circuits Syst., 49(17): 1063-1064. Valashani, M. A., & Mirzakuchaki, S. 2016. A novel fast, low-power and high-performance XORXNOR cell. IEEE Int. Symp. Circuits Syst., 42(4): 694-697. Zavarei, M. J., Baghbanmanesh, M. R., Karaganov, E., Nabovati, H., & Golmakani, A. 2011. Design of new full adder cell using hybrid-CMOS logic style. 'In IEEE International Conference’ at India, during. December 11-12. Zhang, M., Gu, J., & Chang, C. H. 2003. A novel hybrid pass logic with static CMOS output drive fulladder cell. IEEE Int. Symp. Circuits syst., 5(1): 5-8 PATENT SEARCH REPORT A thorough search over available search engines revealed that there are no patents as such found on the topic “Design and Analysis of 1-bit Full Adder using CMOS 45nm Technology.” Km Shweta Bhandari Dr. Abhishek Tomar Student ID: 59586 Advisor M. Tech. (E&C) Department of E&CE