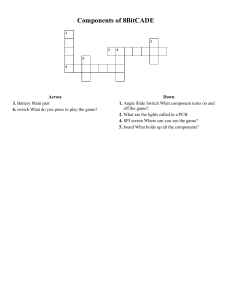

BECE399J Summer Industrial Internship SERIAL PERIPHERAL INTERFACE DESIGN U Sai Kiran 21BEC1188 INDUSTRY COMPLETE ADDRESS & CONTACT PERSONS WITH PHONE NUMBERS Address: 21/1A, III Floor, Marudhar Avenue, Gottigere Uttarahalli Hobli, South Taluk, Bannerghatta Main Rd, Bengaluru, Karnataka 560076 Contact: 080 6909 6300 2 CERTIFICATES FOR DESIGN METHODOLOGIES: 3 Certificates For Internship : 4 Agenda About the company Objective of the Training Overview of the Project Proposed system About Blocks and sub blocks Results and discussions Conclusion References 5 • About the Company Maven Silicon is a distinguished company in the domain of VLSI (Very Large Scale Integration) design and semiconductor technology. It has established itself as a leading institution that offers a wide array of services and training programs related to VLSI design and verification. • One of the standout features of Maven Silicon is its comprehensive VLSI training programs. These programs cover a wide spectrum of topics, from the fundamentals of digital design to advanced concepts such as ASIC and FPGA design. This ensures that students are not only taught theoretical concepts but also gain insights into the latest industry trends and best practices • Maven Silicon's commitment to quality education is underscored by its industry-recognized certifications, which serve as a testament to the skills and knowledge acquired during the training programs. 6 Objective of the Training WISHBONEMASTER SPI MASTER CORE SPI SERIAL SLAVE The VLSI Design Methodologies Course by MAVEN SILICON provided an overview of VLSI and explains various VLSI technology Following project assignment, each student received project-specific training. In this case, detailed concepts of SERIAL PERIPHERAL INTERFACE(DESIGN). 7 Overview of the Project The project focuses on creating an SPI system with a clock generator and Wishbone interface to ensure proper synchronization, timing, and seamless integration with other system components. The SPI system consists of a master device and slave devices, which communicate using a master-slave architecture. The master device generates the clock signal, controls the communication, and features a shift register for transmitting and receiving data. The slave devices respond to commands from the master and send or receive data accordingly. The clock generator is responsible for generating the SCLK (Serial Clock) signal, which synchronizes data transfer between the master and slave devices. The clock generator's functionality includes clock frequency generation, clock polarity control, clock phase control, clock synchronization, clock division, and clock enable/disable. 8 The master device is connected to a Wishbone interface, which is a popular open-source bus architecture used for interconnecting IP cores in a system-onchip design. The Wishbone interface provides a standardized method for communication between different IP blocks within the system. By connecting the SPI master to the Wishbone interface, the system benefits from a modular and scalable design, allowing for efficient data exchange between the SPI master and other components connected to the Wishbone bus. The project also includes a detailed description of the SPI core, clock generator, and shift register, along with their respective block diagrams, functionality, and outputs. The SPI core is responsible for the overall SPI communication, while the clock generator and shift register handle clock signal generation and data transmission/reception, respectively. In conclusion, this project report presents the design and implementation of an SPI system with a clock generator and Wishbone interface, providing a comprehensive solution for synchronous serial communication in embedded systems. 9 Proposed System 10 The SPI system consists of two main components: the master device and the slave devices.where the master controls communication and the slaves respond to commands. The master device generates a clock signal (SCLK) for synchronization and coordinates data transfer. Slave devices receive commands from the master, send data back (MISO), and are selected using SS/CS signals when multiple slaves are present. A clock generator in the master device generates the SCLK signal for timing data transmission. The master device includes a shift register for shifting out transmitted data and receiving data from slave devices. Integration with other components is facilitated by connecting the master device to a Wishbone interface, a standard bus architecture for communication in system-on-chip designs. The Wishbone interface allows for modular and scalable design, enabling efficient data exchange between the SPI master and other components connected to the Wishbone bus. 11 SPI OVERALL MODULE: 12 WISHBONE MASTER – SPI MASTER: • The Wishbone master in this project serves as the central component that initiates and controls communication with peripheral devices. • It is responsible for generating and managing the Wishbone signals to enable data transfer between the SPI module and other components in the system. • The Wishbone master incorporates a clock generator to generate the necessary clock signals for synchronization. • It utilizes the Wishbone interface to seamlessly integrate the SPI functionality into a larger system, allowing for efficient data exchange between the SPI master and other components connected to the Wishbone bus. • The modular and scalable design of the Wishbone master enables easy integration with various IP cores, enhancing the overall functionality and flexibility of the system. 13 WISHBONE INTERFACE SIGNALS: WB_CLK_I: Connects Wishbone clock signal to SPI clock (SCLK) for synchronized data transfers. WB_RST_I: Connects Wishbone reset signal to reset input of SPI module for initialization or resetting. WB_CYC_I: Connects Wishbone cycle signal to SPI chip select (SS/CS) for indicating start of a bus cycle. WB_STB_I: Connects Wishbone strobe signal to SPI chip select (SS/CS) for indicating start of a bus transfer. WB_WE_I: Connects Wishbone write-enable signal to SPI module's write enable input for specifying write or read operation. WB_SEL_I: Connects Wishbone select signal to SPI module's slave select (SS/CS) for selecting appropriate slave device. WB_ADRI: Connects Wishbone address signal to SPI module's address inputs for specifying data location. WB_DAT_I: Connects Wishbone data input signal to SPI module's data input (MOSI) for transferring data from Wishbone to SPI module during write operations. WB_DAT_O: Connects Wishbone data output signal to SPI module's data output (MISO) for transferring data from SPI module to Wishbone during read operations. WB_ACK_O: Connects SPI module's acknowledgment signal to Wishbone acknowledgment signal for indicating successful bus transfer. WB_ERR_O: Connects SPI module's error signal to Wishbone error signal for indicating any error during the SPI transaction. 14 SPI MASTER – SPI SLAVE: he SPI master in this project serves as the primary controller that initiates and manages communication with slave devices. It generates the clock signal (SCLK) for synchronization and coordinates the data transfer between the master and slave devices. The SPI master features a shift register for sequentially shifting out data to be transmitted and receiving data from slave devices. It utilizes separate data lines (MOSI and MISO) for full-duplex communication, allowing data to be sent and received simultaneously. It implements error detection and correction mechanisms to ensure reliable data transmission and communication integrity. 15 SPI EXTERNAL CONNECTIONS: 1.SCLK_PAD_O (Serial Clock): The master generates the clock signal that synchronizes data transfer between the master and slave devices. The SCLK_PAD_O signal must be connected from the master to all the slave devices. 2.MOSI_PAD_O (Master Output, Slave Input): The master sends data to the slave devices on the MOSI line. This line carries the data from the master to the selected slave device(s). 3.MISO_PAD_I (Master Input, Slave Output): The slave devices send data back to the master on the MISO line. This line carries the data from the selected slave device(s) to the master. 4.SS_PAD_O (Slave Select/Chip Select): The SS/CS line is used to select a specific slave device for communication when multiple slave devices are connected. Each slave device typically has its own SS/CS line connected to the master, allowing individual selection. 16 CORE REGISTER LIST: All registers are 32-bit wide and accessible only with 32 bits (all wb_sel_i signals must be active). Data receive registers [RxX]: Hold received data of the last executed transfer. Valid bits depend on the character length field in the CTRL register. Data transmit register [TxX]: Hold data to be transmitted in the next transfer. IE: If set, the interrupt output is set active after a transfer is finished. LSB: Determines whether the LSB or MSB is transmitted/received first. Tx_NEG: Determines the edge of the clock signal for changing the mosi_pad_o signal. Rx_NEG: Determines the edge of the clock signal for latching the miso_pad_i signal. GO_BSY: Writing 1 starts the transfer and remains set during the transfer, automatically cleared after the transfer is finished. CHAR_LEN: Specifies how many bits are transmitted in one transfer (up to 128 bits). DIVIDER REGISTER [DIVIDER]: Specifies the frequency divider of the system clock wb_clk_i to generate the serial clock. SLAVE SELECT REGISTER [SS]: Controls the assertion of ss_pad_o lines based on CTRL[ASS] bit status. 17 OUTPUTS: 18 WISHBONE MASTER WAVEFORM : 19 SPI CORE: 20 MISO OUTPUT WAVEFORM: 21 SLAVE WAVEFORM : 22 CLOCK GENERATOR: • • • • • • • • • The SPI (Serial Peripheral Interface) clock generator is responsible for generating the clock signal (SCLK) used in SPI communication. It provides the timing reference for data transfer between the SPI master and slave devices. Here's an explanation of the signals associated with the SPI clock generator: wb_clk_in: Clock input to the SPI clock generator wb_rst: Reset input for the SPI clock generator go: Input to initiate or trigger the generation of the SCLK signal tip: Output indicating the start or completion of a data transfer last_clk: Output indicating the last clock cycle of a data transfer divider: Input determining the clock frequency of the generated SCLK signal sclk_out: Output representing the generated SCLK signal cpol_0 and cpol_1: Clock polarity options for customizing the clock signal's idle state 23 SHIFT REGISTER: • • • • • • • • • • • • • • • • • tx_negedge: Input triggering data shifting on falling edge of clock signal rx_negedge: Input triggering data sampling on falling edge of clock signal byte_sel: Input selecting byte-by-byte or continuous data shifting latch: Input capturing or storing data from shift register len: Signal specifying length of bits to be shifted in or out p_in: Parallel data input to the shift register wb_clk_in: Clock input to the SPI shift register wb_rst: Reset input for the SPI shift register go: Input initiating or triggering data transfer process miso: Output representing the Master In, Slave Out line lsb: Signal determining the bit order of data transfer sclk: Clock output from the SPI shift register cpol_0 and cpol_1: Clock Polarity options for customizing the clock signal's idle state p_out: Parallel data output from the shift register last: Signal indicating the last transfer in a sequence mosi: Input representing the Master Out, Slave In line tip: Signal indicating the start or completion of a data transfer 24 OUTPUT: • Output of clock generator: 25 • Output of shift register: 26 • Final output: 27 Conclusion The top module along with the sub blocks was successfully implemented and designed using MODELSIM and the block diagrams for the same were made successfully 28 Learning Outcome • Understanding of SPI Communication: A thorough understanding of the SPI communication protocol, its architecture, and its components, including the master device, slave devices, serial data lines, and clock generator. • Clock Generator Design: Knowledge of designing a clock generator for generating the SCLK (Serial Clock) signal, which synchronizes data transfer between the master and slave devices. This includes understanding clock frequency generation, clock polarity control, clock phase control, clock synchronization, clock division, and clock enable/disable. 29 Shift Register Functionality: Familiarity with the operation and functionality of a shift register, which is responsible for sequentially shifting out the data to be transmitted and receiving data from the slave devices. Wishbone Interface Integration: Understanding of how to integrate the SPI system with a Wishbone interface, a popular open-source bus architecture used for interconnecting IP cores in a system-on-chip design. This includes learning how to enable efficient data exchange between the SPI master and other components connected to the Wishbone bus. Problem-solving and Critical Thinking: The ability to analyze complex problems, design solutions, and evaluate their effectiveness, which are essential skills for engineering and technology professionals. 30 Future Scope • There are several potential future developments and enhancements for the SPI system design described in the provided project report. These include: • Multi-Slave Interface: Enhancing the system to support multiple slave devices, allowing for communication with multiple peripherals simultaneously. • Enhanced Clock Generator: Improving the clock generator to provide even more flexible clock signal generation capabilities, such as support for additional clock phases and synchronization techniques. • Higher-Speed Data Transmission: Developing strategies to increase the data transmission speed, which could be achieved through techniques such as buffering, error checking, and over-sampling. 31 References 1."SPI Master/Slave Implementation on an FPGA" by Ahmad Ibrahim, Rami M. Mahmoud, and Mohammed A. Al-Rababaa. (Date: 2016) 2."Design and Implementation of SPI Communication in FPGA" by Ashwini S. Bhosale and Prof. S. D. Lokhande. (Date: 2015) 3."Design and Implementation of SPI Master Controller Using VHDL" by Pooja N. Mali and Prof. S. D. Lokhande. (Date: 2014) 4."A High-Speed SPI Controller Design Using VHDL" by Anu Vijayakumar and S. Mythili. (Date: 2017) 5."Implementation of SPI Protocol in VHDL" by Amandeep Kaur and Navneet Kaur. (Date: 2018) 32