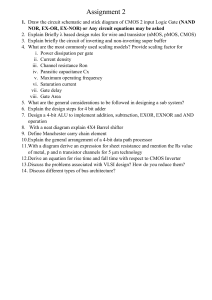

VLSI Design: Introduction to Very Large Scale Integration

advertisement