Programas Verilog: Circuitos Combinacionales y Secuenciales

advertisement

Verilog Programs

Combinational circuits

Inverter

moduleinv (F,x);

input x;

output F;

assign F = ~x;

endmodule

Input OR gate

module or_2 (F,x,y);

inputx,y;

output F;

assign F = x | y;

endmodule

Input NOR gate

module nor_2 (F,x,y);

inputx,y;

output F;

assign F = ~ (x | y);

endmodule

Input AND gate

module and_2 (F,x,y);

inputx,y;

output F;

assign F = x & y;

endmodule

Input NAND gate

module nand_2 (F,x,y);

inputx,y;

output F;

assign F = ~ (x & y);

endmodule

Input XOR gate

module xor_2 (F,x,y);

inputx,y;

output F;

assign F = x ^ y;

endmodule

Input XNOR gate

module xnor_2 (F,x,y);

inputx,y;

output F;

assign F = ~ (x ^ y);

endmodule

Half adder

moduleh_adder(s,c,a,b);

inputa,b;

outputs,c;

assign s=a^b;

assign c=a&b;

endmodule

Full adder

modulef_adder ( sum,cout,a,b,cin );

outputsum,cout;

inputa,b,cin;

assign sum = a ^ b ^ cin;

assigncout = (a&b) | (b&cin) |

(cin&a);

endmodule

Half subtractor

modulehalf_subtractor(d,b,i1

,i2);

outputd,b;

input i1,i2;

assign d=i1^i2,b=(~i1)&i2;

endmodule

Full subtractor

modulefull_subtctor(b,d,i1,i2,i

3);

input i1,i2,i3;

outputb,d;

assign

d=i1^i2^i3,b=((~i1)&i2)|(i2&i

3)|(i3&(~i1));

endmodule

Ripple carry adder

module ripple(X, Y, S, Co);

input [3:0] X, Y;

output [3:0] S;

output Co;

wire w1, w2, w3;

fulladder u1(X[0], Y[0], 1'b0,

w1);

fulladder u2(X[1], Y[1], w1,

w2);

fulladder u3(X[2], Y[2], w2,

w3);

fulladder u4(X[3], Y[3], w3,

Co);

endmodule

BCD adder

modulebcd_adder(a,b,carry_

in,sum,carry);

input [3:0] a,b;

inputcarry_in;

output [3:0] sum;

output carry;

reg [4:0] sum_temp;

reg [3:0] sum;

reg carry;

always @(a,b,carry_in)

Multiplexer 4:1

module mux41(y,s,a,en);

input [1:0]s;

input [3:0]a;

inputen;

output y;

reg y;

always@(s,a)

begin

if(en)

begin

S[0],

S[1],

S[2],

S[3],

Multiplexer 8:1

module mux81(y1,y2,y3,[0:7]i,en);

output y1,y2,y3;

inputen;

input [0:7]i;

wire y1,y2;

reg y3;

always@(en,i,sel)

if(en==0)

begin

mux41 a(y1,[0:3]i,[0:1]sel);

begin

sum_temp = a+b+carry_in;

if(sum_temp> 9) begin

sum_temp = sum_temp+6;

carry = 1;

sum = sum_temp[3:0]; end

else begin

carry = 0;

sum = sum_temp[3:0];

end

end

endmodule

case(s)

Demultiplexer 8:1

module demux18(d,s,y);

input d;

input [2:0]s;

input [7:0]y;

reg [7:0]y;

always@ (d or s)

begin

case(s)

3’b000:

y<={1’b0,1’b0,1’b0,1’b0,1’

b0,1’b0,1’b0, d};

3’b001:

y<={1’b0,1’b0,1’b0,1’b0,1’

b0,1’b0,d,1’b0};

3’b010:

y<={1’b0,1’b0,1’b0,1’b0,1’

b0,d,1’b0,1’b0};

3’b011:

y<={1’b0,1’b0,1’b0,1’b0,d,1

’b0,1’b0,1’b0};

3’b100:

y<={1’b0,1’b0,1’b0,d,1’b0,1

’b0,1’b0,1’b0};

3’b101:

y<={1’b0,1’b0,d,1’b0,1’b0,1

’b0,1’b0,1’b0};

3’b110: y<={1’b0,d,

1’b0,1’b0,1’b0,1’b0,1’b0,1’

b0};

3’b111: y<={d,

1’b0,1’b0,1’b0,1’b0,1’b0,1’

b0,1’b0};

endcase

end

endmodule

Encoder

module prien_4x2(a,y);

input [3:0]y;

output [1:0]a;

reg [1:0]a;

always@(y)

begin

casex(a)

4'b1000:a<=2'b00;

4'bx100:a<=2'b01;

4'bxx10:a<=2'b10;

4'bxxx1:a<=2'b11;

default:a<=2'bzz;

endcase

end

endmodule

2'b00:y<=a[3];

2'b01:y<=a[2];

2'b10:y<=a[1];

2'b11:y<=a[0];

endcase

end

else

y<=1'bx;

end

endmodule

else

mux41 b(y2,[4:7]i,[0:1]sel);

end

or y(y3,y2,y1);

endmodule

Decoder

module dec_3x8(d,i);

input [2:0]i;

output [7:0] d;

reg [7:0]d;

always @(i)

begin

if(i==3'b000)

d<=8'h80;

else if(i==3'b001)

d<=8'h40;

else if(i==3'b010)

d<=8'h20;

else if(i==3'b011)

d<=8'h10;

else if(i==3'b100)

d<=8'h08;

else if(i==3'b101)

d<=8'h04;

else if(i==3'b110)

d<=8'h02;

else if(i==3'b111)

d<=8'h01;

else

d<=8'bzzzzzzzz;

end

endmodule

Sequential circuits

D Flip flop

moduledff(q,qb,clk,d,rst);

inputclk,d,rst;

outputq,qb;

regq,qb;

always @(posedgeclk or

negedgerst)

begin

if(!rst)

begin

q<=1'b0;

qb<=1'b1;

end

else

begin

q=d;

qb=~d;

end

end

endmodule

T Flip flop

moduletff(q,qb,clk,t,rst);

inputclk,t,rst;

outputq,qb;

regq,qb;

always @(posedgeclk or negedgerst)

begin

if(!rst)

begin

q<=1'b0;

qb<=1'b1;

end

else

begin

if(t==1'b0)

begin

q=q;

qb=~q;

end

else if(t==1'b1)

begin

q=~q;

qb=~q;

end

else

begin

q=1'b0;

qb=~q;

end

end

end

endmodule

JK Flip flop

modulejff(q,qb,clk,j,k,rst);

inputclk,j,k,rst;

outputq,qb;

regq,qb;

always@(posedgeclk

or

negedgerst)

begin

if(!rst)

begin

D latch

module dl(q, qb,en,d,rst);

inputen,d,rst;

outputq,qb;

regq,qb;

always @(en or rst)

begin

if(!rst)

begin

q<=1'b0;

SR Flip flop

modulesff(q,qb,clk,s,r,rst);

inputclk,s,r,rst;

outputq,qb;

regq,qb;

always @(posedgeclk or

negedgerst)

begin

if(!rst)

begin

q<=1'b0;

qb<=1'b1;

end

else

begin

if((s==1'b0)&&(r==1'b0))

begin

q=q;

qb=~q;

end

else if((s==1'b0)&&(r==1'b1))

begin

q=1'b0;

qb=~q;

end

else if((s==1'b1)&&(r==1'b0))

begin

q=1'b1;

qb=~q;

end

else if((s==1'b1)&&(r==1'b1))

begin

q=1'bx;

qb=1'bx;

end

else

begin

q=1'b0;

qb=~q;

end

end

end

endmodule

T Latch

moduletl(q,qb,en,t,rst);

inputen,t,rst;

outputq,qb;

regq,qb;

always @(en or rst)

begin

if(!rst)

begin

q<=1'b0;

q<=1'b0;

qb<=1'b1;

end

else

begin

if((j==1'b0)&&(k==1'b0))

begin

q=q;

qb=~q;

end

else

if((j==1'b0)&&(k==1'b1))

begin

q=1'b0;

qb=~q;

end

else

if((j==1'b1)&&(k==1'b0))

begin

q=1'b1;

qb=~q;

end

else

if((j==1'b1)&&(k==1'b1))

begin

q=~q;

qb=~q;

end

else

begin

q=1'b0;

qb=~q;

end

end

end

endmodule

qb<=1'b1;

end

else

begin

if(en)

begin

q=d;

qb=~d;

end

end

end

endmodul

SR Latch

Module sl(q,qb,en,s,r,rst);

inputen,s,r,rst;

outputq,qb;

regq,qb;

always @(en or rst)

begin

if(!rst)

begin

q<=1'b0;

qb<=1'b1;

end

else

begin

if(en)

begin

if((s==1'b0)&&(r==1'b0))

begin

JK Latch

Module jl(q,qb,en,j,k,rst);

inputen,j,k,rst;

outputq,qb;

regq,qb;

always @(en or rst)

begin

if(!rst)

begin

q<=1'b0;

qb<=1'b1;

end

else

begin

if(en)

begin

if((j==1'b0)&&(k==1'b0))

begin

PIPO

modulepipo(q,d,clk);

inputclk;

input [3:0]d;

output [3:0]q;

dff d1(q[3],d[3],clk);

dff d2(q[2],d[2],clk);

dff d3(q[1],d[1],clk);

dff d4(q[0],d[0],clk);

endmodule

qb<=1'b1;

end

else

begin

if(en)

begin

if(t==1'b0)

begin

q=q;

qb=~q;

end

else if(t==1'b1)

begin

q=~q;

qb=~q;

end

else

begin

q=1'b0;

qb=~q;

end

end

end

end

endmodule

SISO

modulesiso(q,d,clk);

inputd,clk;

output q;

wire a[2:0];

dff d1(a[2],d,clk);

dff d2(a[1],a[2],clk);

dff d3(a[0],a[1],clk);

dff d4(q,a[0],clk);

endmodule

SIPO

modulesipo(q,clk,din,rst);

inputclk,din,rst;

output [3:0]q;

initial q=4’b0000;

reg [3:0]q;

always@(posedgeclk)

begin

if(!rst)

q<=4'b0000;

else

q<={q[2:0],din};

end

endmodule

PISO

modulepiso(clk,rst,a,q);

inputclk,rst;

q=q;

qb=~q;

end

else

if((s==1'b0)&&(r==1'b1))

begin

q=1'b0;

qb=~q;

end

else

if((s==1'b1)&&(r==1'b0))

begin

q=1'b1;

qb=~q;

end

else

if((s==1'b1)&&(r==1'b1))

begin

q=1'bx;

qb=1'bx;

end

else

begin

q=1'b0;

qb=~q;

end

end

end

end

endmodule

Up down counter

modulecntr_ud(clk,sel,clr,Q

);

inputclk,clr,sel;

output [3:0]Q;

reg [3:0]temp;

always @(posedgeclk)

begin

if(clr)

temp<=4’b0000;

else

if(sel==1’b1)

temp<=temp+1’b1;

else

temp<=temp-1’b1;

end

assign Q<=temp;

endmodule

q=q;

qb=~q;

end

else if((j==1'b0)&&(k==1'b1))

begin

q=1'b0;

qb=~q;

end

else if((j==1'b1)&&(k==1'b0))

begin

q=1'b1;

qb=~q;

end

else if((j==1'b1)&&(k==1'b1))

begin

q=~q;

qb=~q;

end

else

begin

q=1'b0;

qb=~q;

end

end

end

end

endmodule

input [3:0]a;

output q;

initial q=4’b0000;

reg q;

reg [3:0]temp;

always@(posedgeclk,posedger

st)

begin

if(rst==1'b1)

begin

q<=1'b0;

temp<=a;

end

else

begin

q<=temp[0];

temp<= temp>>1'b1;

end

end

endmodule

7 Segment

Module sevenseg(a,k);

input [2:0]k;

outputreg [6:0]a;

always @(k)

begin

if(k==3'b000)

a <= 7'b0000001;

else if(k == 3'b001)

a <= 7'b1001111;

else if(k == 3'b010)

a <= 7'b0010010;

else if(k == 3'b011)

a <= 7'b0000110;

else if(k == 3'b100)

a <= 7'b1001100;

else if(k == 3'b101)

a <= 7'b0100100;

else if(k == 3'b110)

a <= 7'b0100000;

else if(k == 3'b111)

a <= 7'b0001111;

end

endmodule

ALU

Module alua(o,s,a,b);

output [0:7]o;

input [0:1]s;

input [0:3]a;

input [0:3]b;

reg [0:7]o;

always @(a,b,s)

begin

case(s)

3'b00:o<=a+b;

3'b01:o<=a-b;

3'b10:o<=a*b;

3'b11:o<=a/b;

default:o<=8'b00000000;

endcase

end

endmodule

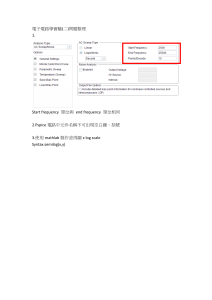

LED blinking

module clock(clko,clki);

inputclki;

outputclko;

regclko=0;

integercnt=0;

always@(posedgeclki)

begin

cnt=cnt+1;

if(cnt==25000000)

begin

clko<=!clko;

cnt=0;

end

end

endmodule

SIPO using bluespec

packageSipo();

(*synthesize*)

modulemksipo();

Reg# (Bit#(1))

sin <- mkReg(1’b0);

Reg# (Bit#(5))

pout <- mkReg(5’b0);

Reg# (UInt#(8))

cnt<- mkReg(8’b0);

rule shift (cnt< 10);

dout<={dout[3:0],sin};

sin<=~sin;

$display(“cnt=%b\n”,dout);

cnt<= cnt + 1;

endrule

rule stop(cnt == 10);

$finish(0);

endrule

endmodule:mksipo

endpackage:Sipo

Memory accessing

module

Memory(addr,data,clko,sen,swen,clk

i);

inputclki;

output [0:17]addr;

outputclko;

output [0:15]data;

outputsen=0;swen=0;

regclko=0;

integer cnt=0;

integer cnt1=0;

assignaddr=cnt;

assign data=cnt;

always@(posedgeclki)

begin

cnt=cnt+1;

if(cnt==2500000)

begin

clko<=!clko;

cnt1=cnt1+1

if(cnt1>=10)

begin

cnt1=0;

end

cnt=0;

end

end

endmodule

Up down counter 4 bit

packageTb_counter;

(*synthesize*)

modulemkcounter();

Reg# (Bit#(4)) cnt<- mkReg(0);

Reg# (Bit#(1)) upd<- mkReg(0);

rule up (upd == 1);

cnt<= cnt + 1;

$display("count = %b",cnt);

endrule rule dwn (upd == 0);

cnt<= cnt - 1;

$display("count = %b",cnt);

endrule

endmodule:mkcounter

endpackage:Tb_counter