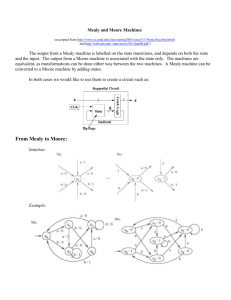

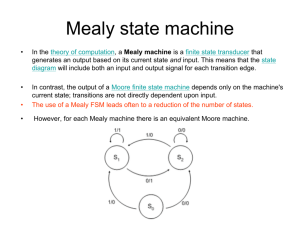

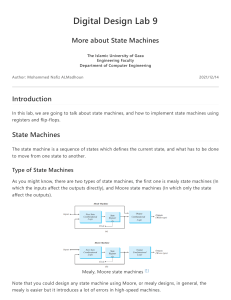

Finite State Machine ITSC-7698 FPGA-FSM By Dr.Vittapu Definition of a State Machine • All programmable logic designs can be specified in Boolean form. • However some designs are easier to conceptualize and implement using nonBoolean models. • The State Machine model is one such model. 2 Definition of a State Machine • A state machine represents a system as a set of states, the transitions between them, along with the associated inputs and outputs. • So, a state machine is a particular conceptualization of a particular sequential circuit. • State machines can be used for many other things beyond logic design and computer architecture. 3 Finite State Machines • Any Circuit with Memory Is a Finite State Machine • Even computers can be viewed as huge FSMs • Design of FSMs Involves • Defining states • Defining transitions between states • Optimization / minimization • Above Approach Is Practical for Small FSMs Only 4 State Machines: Definition of Terms •State Diagram •Illustrates the form and function of a state machine. Usually drawn as a bubble-and-arrow diagram. •State •A uniquely identifiable set of values measured at various points in a digital system. •Next State •The state to which the state machine makes the next transition, determined by the inputs present when the device is clocked. •Branch •A change from present state to next state. •Mealy Machine •A state machine that determines its outputs from the present state and from the inputs. •Moore Machine •A state machine that determines its outputs from the present state only. 5 Finite State Machines • Finite State Machines (FSMs) are a useful abstraction for sequential circuits design • At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state inputs + Combinational Logic present state + next state n n Q CLK outputs Registers D • • • • FSMs: What are they? A method of modeling a system comprised of a limited number of modes of operation. Depending on which mode it is in the machine will behave in one manner or another. Abstraction tool ( an approach to solving more complex problems). An abstract machine that can be in exactly one of a finite number of states at any given time. The FSM can change from one state to another in response to some external inputs. The change from one state to another is called a transition. Simple Design procedure Word Description State transition Diagrams State encoding Next State & output Tables State & output function realization Two Types of FSMs Moore and Mealy FSMs : different output generation • Moore FSM: inputs x0...xn next state S+ Comb. Logic n Q D Comb. Logic Registers CLK outputs yk = fk(S) n present state S • Mealy FSM: direct combinational path! inputs x0...xn Comb. Logic S+ n D Comb. Logic Q Registers CLK n S outputs yk = fk(S, x0...xn) Present State and Next State State 4 State 5 State 6 • For any given state, there is a finite number of possible next states. On each clock cycle, the state machine branches to the next state. One of the possible next states becomes the new present state, depending on the inputs present on the clock cycle. State 7 On a well-drawn state diagram, all possible transitions will be visible, including loops back to the same state. From this diagram it can be deduced that if the present state is State 5, then the previous state was either State 4 or 5 and the next state must be either 5, 6, or 7. 10 Moore and Mealy Machines • Both these machine types follow the basic characteristics of state machines, but differ in the way that outputs are produced. • Moore Machine: • Outputs are independent of the inputs, ie outputs are effectively produced from within the state of the state machine. • Mealy Machine: • Outputs can be determined by the present state alone, or by the present state and the present inputs, ie outputs are produced as the machine makes a transition from one state to another. 11 Machine Models Inputs Inputs Combinatorial Logic to Determine State Combinatorial Logic to Determine State Present State Register Bank Present State Register Bank Combinatorial Logic to Determine Output Based on: Present State Combinatorial Logic to Determine Output Based on: Present State Present Inputs Moore Machine Output Mealy Machine Output 12 Moore Machine Diagrams The Moore State Machine output is shown inside the state bubble, because the output remains the same as long as the state machine remains in that state. The output can be arbitrarily complex but must be the same every time the machine enters that state. Output condition that results from being in a particular present state State 1 q,r i,j a,b Input condition that must exist in order to execute these transitions from State 1 State 2 x,y 13 Mealy Machine Diagrams The Mealy State Machine generates outputs based on: The Present State, and The Inputs to the M/c. So, it is capable of generating many different patterns of output signals for the same state, depending on the inputs present on the clock cycle. Outputs are shown on transitions since they are determined in the same way as is the next state. Output condition that results from being in a particular present state State 1 i,j x,y a,b q,r Input condition that must exist in order to execute these transitions from State 1 State 2 14 Moore Machine • Describe Outputs as Concurrent Statements Depending on State Only transition condition 1 state 1 / output 1 state 2 / output 2 transition condition 2 15 Mealy Machine • Describe Outputs as Concurrent Statements Depending on State and Inputs transition condition 1 / output 1 state 2 state 1 transition condition 2 / output 2 16 Moore vs. Mealy FSM (1) • Moore and Mealy FSMs Can Be Functionally Equivalent • Mealy FSM Has Richer Description and Usually Requires Smaller Number of States • Smaller circuit area 17 Moore vs. Mealy FSM (2) • Mealy FSM Computes Outputs as soon as Inputs Change • Mealy FSM responds one clock cycle sooner than equivalent Moore FSM • Moore FSM Has No Combinational Path Between Inputs and Outputs • Moore FSM is less likely to have a shorter critical path 18 Moore FSM - Example 1 • Moore FSM that Recognizes Sequence 10 0 1 S0 / 0 reset Meaning of states: S0: No elements of the sequence observed 1 0 S1 / 0 0 S1: “1” observed 1 S2 / 1 S1: “10” observed 19 Mealy FSM - Example 1 • Mealy FSM that Recognizes Sequence 10 0/0 1/0 S0 reset Meaning of states: 1/0 S1 0/1 S0: No elements of the sequence observed S1: “1” observed 20 Moore & Mealy FSMs – Example 1 clock 0 1 0 0 0 S0 S1 S2 S0 S0 S0 S1 S0 S0 S0 input Moore Mealy 21 Finite State Machine (FSM) 0 00/0 1 0 0 01/0 1 0 11/0 1 =Oפלט 10/1 1 • Moore FSM 22 Finite State Machine (FSM) 0/0 00 1/0 0/0 0/0 01 1/0 0/0 10 1/1 פלט 11 1/1 • Mealy FSM 23 0 00/0 1 01/0 1 11/0 1 0 10/1 0 0 At 0 0 1 1 Bt 0 1 1 0 I=0 I=1 At+1 Bt+1 At+1 Bt+1 0 0 0 1 0 0 1 1 0 0 1 0 0 0 1 0 Ot 0 0 0 1 1 24 At 0 0 1 1 Bt 0 1 0 1 X=0 X=1 X=0 X=1 At+1 Bt+1 At+1 Bt+1 Ot Ot 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 1 0 0 1 1 0 1 25 0 00/0 1 0 At 0 0 1 1 01/0 1 11/0 1 0 0 10/1 I=0 I=1 At+1 Bt+1 At+1 Bt+1 0 0 0 1 0 0 1 1 0 0 1 0 0 0 1 0 Bt 0 1 1 0 Ot 0 0 0 1 1 AB Bt+1 0 1 00 01 AB 11 10 I At+1 0 1 00 01 11 10 26 I D A Q Q’ O D B Q Q’ At+1= A*I + B * I= I(A+B) Bt+1= A*I O = A*B 27 D A Q Q’ X Out D B Q Q’ • QA ,QB - וX. 28 Mealy Vs Moore • They differ only in how the output function is computed • Moore: Output values are a function of the state only • Mealy: Output Values are generated based on both the state of the circuit and the present values of its inputs. • Both are considered to have similar computation capability, although Mealy machine normally accomplishes the same task with fewer states. • But, when the FSM is used as a control circuit, Moore approach provides safer control signal timing. Moore vs. Mealy FSMs Consider a snail that crawls down a paper tape with 1’s and 0’s on it. The snail smiles whenever the last four digits it has crawled over are 1101. • Design Moore and Mealy FSMs of the snail’s brain. • Write Verilog code for your Moore and Mealy FSMS. State Transition Diagrams: Looking for 1 “1101” 0 0 1 S0 0 1 S1 0 1 S2 0 0 1 S3 0 0 S4 1 0 Moore Machine: States indicate output 0/0 S0 1/1 0/0 1/0 S1 1/0 S2 1/0 0/0 S3 0/0 Mealy Machine: Arcs indicate input/output Moore Machine S S0 S0 S1 S1 S2 S2 S3 S3 S4 S4 Next State A S’ 0 1 0 1 0 1 0 1 0 S0 S1 S0 S2 S3 S2 S0 S4 S0 1 S2 Output S Y S0 S1 S2 S3 S4 0 0 0 0 1 Moore Machine A S‘ 2 Next State S A S’ 000 000 001 001 010 010 011 011 100 100 0 1 0 1 0 1 0 1 0 1 000 001 000 010 011 010 000 100 000 010 Output S Y 000 001 010 011 100 0 0 0 0 1 S2 CLK S‘ 1 S1 CLK S‘ 0 CLK S0 Y Mealy Machine S A S’ Y S0 S0 S1 S1 S2 S2 S3 S3 0 1 0 1 0 1 0 1 S0 S1 S0 S2 S3 S2 S0 S1 0 0 0 0 0 0 0 1 Mealy Machine A S A S’ Y 00 00 01 01 10 10 11 11 0 1 0 1 0 1 0 1 00 01 00 10 11 10 00 01 0 0 0 0 0 0 0 1 S‘ S1 1 CLK S‘ 0 CLK Y S0 More Intuitive Solutions using Shift Registers Y A CLK Mealy Form: Output Depends on Input Immediately Y A CLK Moore Form: Output Depends Only on State Exercise Consider a snail that crawls down a paper tape with 1’s and 0’s on it. The snail smiles whenever it detects two consecative ones. • Design Moore and Mealy FSMs of the snail’s brain. • Write Verilog code for your Moore and Mealy FSMS. Exercise: Detect consicative 1’s Moor Verilog FSM: Detect consicative 1’s FSM Issues 1. Power on Reset 2. The clock Frequency Then we started which some issues and the finite state machine are the controller. We have looked at how to bring the state machine to a starting state using a reset very simple thing. So, you should not forget to bring the state machine it was starting state by you know putting the reset, second thing we have looked at is what is the kind of most appropriate clock frequency for a controller for a state machine. We have looked at the maximum frequency but then that is not a good idea to run the state machine has the maximum frequency it dissipate lot of power, suppose the data path is running at a much lower frequency. So, what should be the kind of how much you can bring down the clock frequency of the state machine o So, this is the slide on power on reset. So, this is the state machine you know kind of structure. o You have the flip-flops which gives the present state, and that combine with the input will, you know give the next state using next state logic. o The present state is decoded to produce the outputs, some time, some output maybe just a function of present state, and some output could be a function of the present state and input. 2. Clock frequency issue There are the clock period we use a maximum time delay and for the hold old time violation. We use the minimum delays okay, because it is the hold time violation happens with the same edge. the maximum clock frequency. But then we set there is no kind of point in clocking at the maximum clock frequency, because it dissipates lot of power and more over.