cmos-vlsi-design-a-circuits-and-systems-perspective-4th-edition-solution

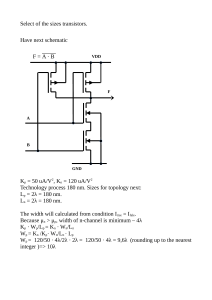

advertisement