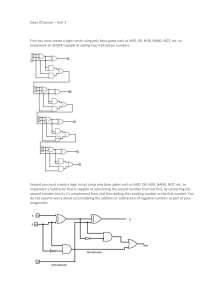

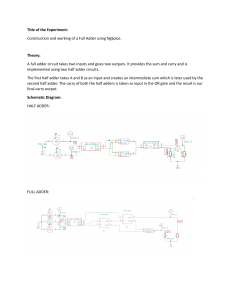

SET Based LOW –POWER AND HIGH-SPEED FULL ADDER USING XOR-XNOR GATES Prepared By: Akash Ghosh (20MVD0143) Under the guidance of: Dr. AARTHY M Associate Professor SENSE, VIT Vellore Objective: To design high speed, low power Full Adder circuits. To do the comparative study of performance analysis of different logic style. Will analyses, evaluates and compares the performance of various adder circuits. To compare the simulation results obtained from conventional circuit with proposed circuit . Literature Review(1/2) Article Title Author Name Date of Observations Publication Low-Power and Fast Full Adder by Exploring New XOR and XNOR Gates Hamed Naseri, Somayeh Timarchi 16 April, 2018 In this paper, novel circuits for XOR/XNOR and simultaneous XOR–XNOR functions are proposed. The proposed circuits are highly optimized in terms of the power consumption and delay, which are due to low output capacitance and low shortcircuit power dissipation. We also propose six new hybrid1-bit full-adder (FA) circuits based on the novel full-swing XOR– XNOR or XOR/XNOR gates. Each of the proposed circuit has its own merits in terms of speed, power consumption, power delay product (PDP), driving ability, and so on. To investigate the performance of the proposed designs, extensive HSPICE and Cadence Virtuoso simulations are performed. The simulation results, based on the 65-nm CMOS process technology model, indicate that the proposed designs have superior speed and power against other FA designs. Design of Swing Dependent XOR-XNOR Gates based Hybrid Full Adder P. Malini, G. Naveen Balaji, K. Boopathi raja, A. Gautami, P. Shanmugavadivu, S. Chenthur Pandian 06 June 2019 They represent full adder using Advanced EXOR-EXNOR circuit to get more efficient result in terms of power, delay. In conventional the draw back is the feedback increase the delay. At that point the advanced EXOR (or) EXNOR and EXOR– EXNOR gates, they recommended that the referenced weaknesses are completely absent. Literature Review(2/2) Article Title Author Name Date of Publication Observations High-Speed Hybrid-Logic Full Adder Using High-Performance 10-T XOR–XNOR Cell Jyoti Kandpal, Abhishek Tomar, Mayur Agarwal and K. K. Sharma 15 April 2020 In this article, a new 10-T XOR–XNOR circuit was proposed which provided full swing outputs simultaneously. Using the proposed XOR–XNOR circuit, four new FA cells based on hybrid logic design style were also proposed. The performance of the proposed XOR–XNOR circuit and the FA cells was tested by simulating them in virtuoso tool of cadence using GPDK90 nm CMOS technology. The proposed XOR–XNOR circuit showed a reduction in terms of delay and PDP up to 65.16%and 70.13%, respectively, than those of other designs. The proposed FA design-4 showed 28%–45% improvement in terms of PDP than that of available FAs. Design of High-Speed Hybrid Full Adders using FinFET 18nm Technology Apoorva Raghunandan, Shilpa D R 02 March 2020 In this paper three hybrid full-adder circuits based on the novel full-swing XOR–XNOR gates have been designed. The HFA 22T (Hybrid Full Adder with 22 transistors), HFA B 26T(Hybrid Full Adder with 26 transistors and Buffers) and HFA NB26T(Hybrid Full Adder with 26 transistors and New Buffers) have been designed using the Cadence virtuoso tool with 18nm FinFET technology. The simulation results have been performed and the delay of the circuit has been calculated. A considerable reduction of delay has been achieved in comparison to MOSFETs. It has been found out that the HFA NB Methodology Our approach is based on XOR-XNOR design Full Adder Circuit in a single unit. Will implement new proposed Full Adder in SET based circuit. Simulation will be done in Cadence Tool in 45nm Technology. Introduction: Why Full adders are important? Modern portable electronics require: Smaller silicon area. ● Higher speeds. ● Longer battery life. ● More reliability. ● Adders are an extensively used component in data paths. Categorization of Full-Adder The outputs of a 1-b full adder can be generally expressed as ● The three broad categories are as follows A. B. C. XOR–XOR-Based Full Adder XNOR–XNOR-Based FullAdder Centralized Full Adder XOR–XOR-Based Full Adder The general formof this category is expressed as follows XONR–XONR-Based Full Adder Centralized Full Adder Different Logic Styles ● Static CMOS Existence of pMOS which has low mobilitycompared to nMOS ● High Input capacitance. ● ● Complementary Pass Transistor(CPL) Low power consumption. ● Reduced Area(when nMOS only). ● Reduced leakage(fewer PUNs and PDNs). ● Increased delay. ● ● Transmission-gate full adder (TGA) ● Lack driving capability. ● Dynamic CMOS Higher switching activity and lower noise immunity. ● Large portion of the power in driving the clock lines ● More susceptible to leakage ● CMOS FULL ADDER (28T) Circuit Schematic CMOS ADDER Transient Response TG Adder Cell Circuit Schematic TG Adder Cell Transient Response TG Pesudo Adder Cell Circuit Diagram TG Pesudo Adder Cell Transient Response Gate Diffusion Input Full Adder Schematic Gate Diffusion Input Full Adder TransientResponse Work Done So Far (As Presented in review 1) 1) literature Survey. 2) Simulation of conventional Logic Gate in Cadence Tool. 3) Comparison Of the conventional Logic gate in terms of delay and power Work to be completed (As Presented in review 1) 1 ) Will implement the Proposed new adder in SET based Circuit in Cadence Tool. 2)Will do the Comparison between the conventional and proposed Circuit. 3)Will make a Comparison table to see the final result. 4)Report Writing(IEEE Standard). Work Done After Review-1 1)Create SET Symbol using Verilog A code. 2) DID V-I characteristics OF SET. 3) Did SET Based inverter and did dc analysis and transient analysis. 4) Did SET Based Logic Gate Like Nand , NOR to check functionality. 5) Design SET Based Full Adder that consume ultra-low power and low voltage. Introduction to Single Electron Transistor (SET) Schematic of SET SET Symbol Why the Island is called Quantum Dot ? SET Symbol SET Based V_GS VS I_D characteristics SET Based V_GS VS I_D characteristics (Manual ) Click to add text SET Based I_D VS V_GS Characteristics Click to add text SET Based I_D VS V_GS Characteristics (Manual) Click to add text SET BASED INVERTER SET Based INVERTER DC Analysis Click to add text SET Based INVERTER Transient Analysi s Click to add text SET Based NAND Gate Click to add text SET Based NAND Gate Transient Analysi s Click to add text Proposed SET Based Full Adder Cell Circuit at room temperature Proposed SET Based Full Adder Cell Transient Analysis Click to add text Proposed Full Adder Cell using XOR Gate Circuit Diagram Click to add text Proposed Full Adder Cell using XOR Gate Transient Analysis Click to add text Proposed Full Adder Cell using XNOR Gate Circuit Diagram Proposed Full Adder Cell using XNOR Gate Transient Analysis Simulation Result(Comparison Table) Logic Families Power Delay 5.68 uW 83.17 nsec Gate Diffusion Input Full Adder 57.78 uW 105.1 nSec TG Pesudo Adder Cell 127.5 uW 133.4 nSec TG Adder Cell 15.47 uW 35.943 nSec Circuit Modification No-01 (SET Based Full Adder Cell ) 28.03 nW 72.58 pSec Circuit Modification No-02 (XOR Based Full Adder Cell ) Circuit Modification No-03 (XNOR Based Full Adder Cell) 10.114 uW 42.31 nSec 8.4 uW 51.14 nsec CMOS Reference 1) Aarthy M, Sriadibhatla Sridevi, “Design and Analysis Of An Ultra-L ow Power Single Electron Transistor Based Binary Multiplier”, Jour of Adv Research in Dynamical & Control Systems, Vol. 11, Nov 27, 2019. 2) M.venkayya Naidu, Y.sravana Kumar, Alajangi Ramakrishna, “ A 45nm CMOS Technology Exploring low power and Fast 4 bit Full Adder using XOR/XNOR Gates.”, November 2019, IJSDR ,Volume 4, Issue 11. 3) Krishna Chandra, Rajeev Kumar, Shashank Uniyal, Vishal Ramola,” A new design 6T Full Adder Circuit using Novel 2T XNOR Gates”, IOSR Journal of VLSI and Signal Processing (IOSR-JVSP),Volume 5, Issue 3, Ver. I (May - Jun. 2015), PP 63-68,e-ISSN: 2319 – 4200, pISSN No. : 2319 – 4197. 4) Subodh Wairya, Rajendra Kumar Nagaria and Sudarshan Tiwari, “Comparative Performance Analysis of XORXNOR Function Based High-Speed CMOS Full Adder Circuits For Low Voltage VLSI Design.”, International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.2, April 2012,DOI : 10.5121/vlsic.2012.3219. 5) Sujatha Hiremath, Deepali Koppad , “Low power full adder circuit using Gate Diffusion Input (GDI) MUX”, Fourth International Conference on Advances in Recent Technologies in Communication and Computing (ARTCom2012), 20 April 2015. Reference 6) Subodh Wairya, Rajendra Kumar Nagaria, Sudarshan Tiwari, "Performance Analysis of High Speed Hybrid CMOS Full Adder Circuits for Low Voltage VLSI Design", Hindawi Publishing Corporation VLSI DesignVolume 2012, Article ID 173079, 18 pages,doi:10.1155/2012/173079. 7) Trapti Sharma, Laxmi Kumre, "A Comparative Performance Analysis of CMOS XOR-XNOR Circuits", Proceeding International conference on Recent Innovations is Signal Processing and Embedded Systems (RISE-2017) 27-29 October,2017. 8) Bhavani Prasad Y, Harish Babu N, Ramana Reddy K.V, Dhanabal R, "Comparative Performance Analysis of XOR-XNOR Function Based High-Speed CMOS Full Adder Circuits", 2014 International Conference on Reliability Optimization and Information Technology (ICROIT). 9) Apoorva Raghunandan, D R Shilpa, "Design of High-Speed Hybrid Full Adders usingFinFET 18nm Technology", 2019 4th International Conference on Recent Trends on Electronics, Information, Communication & Technology (RTEICT). 10) P. Malini, G. Naveen Balaji, K. Boopathiraja, A. Gautami, P. Shanmugavadivu, S. Chenthur Pandian "Design of Swing Dependent XOR-XNOR Gates based Hybrid Full Adder", 2019 5th International Conference on Advanced Computing & Communication Systems (ICACCS). Reference 11) Jyoti Kandpal, Abhishek Tomar, Mayur Agarwal, K. K. Sharma, "High-Speed Hybrid-Logic Full Adder UsingHigh-Performance 10-T XOR–XNOR Cell", IEEE Transactions on Very Large Scale Integration (VLSI) Systems ( Volume: 28, Issue: 6, June 2020). 12) PygastiJuveria, K. Ragini, "Low Power and high Speed Full Adder using newXOR and XNOR Gates", International Journal of Innovative Technology and Exploring Engineering (IJITEE)ISSN: 2278-3075, Volume-8 Issue-8 June, 2019. 13) Hamed Naseri, Somayeh Timarchi "Low-Power and Fast Full Adder by Exploring New XOR and XNOR Gates", IEEE Transactions on Very Large Scale Integration (VLSI) Systems ( Volume: 26, Issue: 8, Aug. 2018). 14) P. Divakara Varma, R.Ramana Reddy, "A Novel 1-Bit Full Adder Design Using DCVSL XOR/XNOR Gate and Pass Transistor Multiplexers", International Journal of Innovative Technology and Exploring Engineering (IJITEE)ISSN: 2278-3075, Volume-2, Issue-4, March 2013. 15) Nabihah Ahmad, Rezaul Hasan, " A New Design of XOR-XNOR gates for low power application", 2011 International Conference on Electronic Devices, Systems & Applications (ICEDSA). Reference 16) Mahapatra, S.; Vaish, V.; Wasshuber, C.; Banerjee, K.; Ionescu, A.M. Analytical modeling of singleelectron transistor for hybrid CMOS-SET analog IC design. IEEE Trans. Electron Devices2004, 51,1772–1782. 17) Uchida, K.; Matsuzawa, K.; Koga, J.; Ohba, R.; Takagi, S.; Toriumi, A. Analytical single-electron transistor (SET) model for design and analysis of realistic SET circuits. Jpn. J. Appl. Phys.2000, 39,2321. 18) G. Manikannan, K. Mahendran, P. Prabakaran, " Low Power High Speed Full Adder Cell with XOR/XNOR Logic Gates in 90nm Technology", 2017 International Conference on Technical Advancements in Computers and Communications (ICTACC), DOI: 10.1109/ICTACC.2017.25,16 October 2017,Melmaurvathur, India. 19) Mahapatra, S.; Ionescu, A.M.; Banerjee, K. A quasi-analytical SET model for fewelectron circuit simulation. IEEE Electron Device Lett.2002, 23, 366–368. 20) Ionescu, A.M.; Mahapatra, S.; Pott, V. Hybrid SETMOS architecture with Coulomb blockade oscillations and high current drive. IEEE Electron Device Lett.2004, 25, 411– 413. 21) Adrian Ionescu, Santanu Mahapatra " Hybrid CMOS Single-Electron-Transistor Device and Circuit Design".