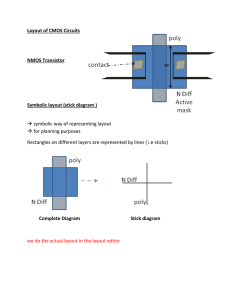

INDIAN INSTITUTE OF VLSI DESIGN AND TRAINING CMOS ASSIGNMENT 1. Draw the cross sectional view and the top view of a CMOS inverter. 2. What is Latch up and its preventive measures? Explain it with the means of diagrams. 3. Explain a. STI b. LOCOS c. Birds beak Effect 4. Explain the following effects a. EM b. ESD c. Antenna Effect d. Body Effect 5. Draw the CMOS inverter characteristics and explain using equations 6. Draw the stick diagram of Inverter and NAND (2 i/p). 7. Explain in brief the various steps of fabrication along with the mask layers. 8. Explain the working of pn junction diode in FB and RB conditions. Also, explain the capacitances in both the cases. 9. What are the advantages and dis-advantages of connecting the substrate of PMOS/NMOS to either of the power rails? 10. What do you mean by pinch off and explain the flow of current after pinch off. 11. What is the use of channel stop implant in the CMOS? 12. Explain DRC, ERC and LVS . What were the errors that you have encountered in your layouts and how did you resolve them? 13. How does the parasitics affect the layout and how do you reduce the effects of parasitics in your layout? 14. Which layout is correct and why? (or) INDIAN INSTITUTE OF VLSI DESIGN AND TRAINING 15. a) When, where and why do we use thin and thick metal layers in layout? b) Which metal layers are used for power rails and why? c) Why do we fix the height in standard cell layouts? d) What are the conventions that have to be followed for standard cell layouts?