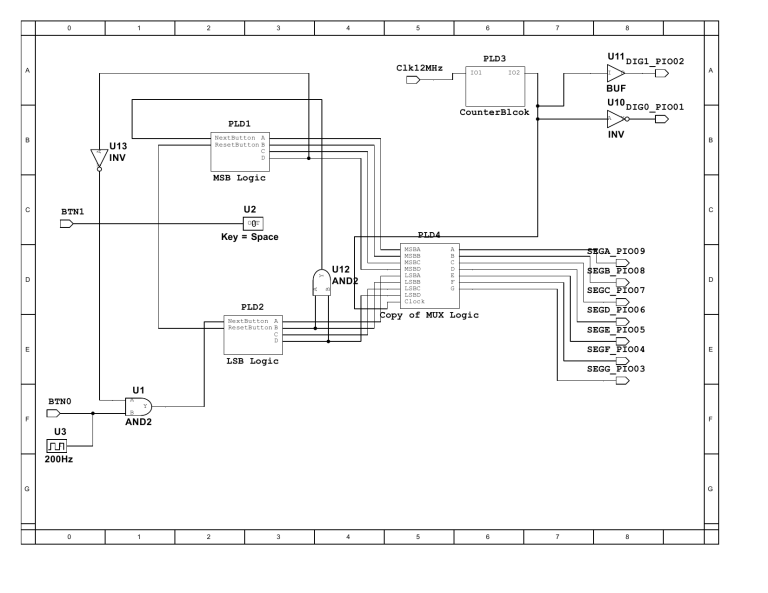

0 1 2 3 4 5 6 IO1 IO2 I CounterBlcok A B Y A A Y INV NextButton A ResetButton B C D U13 INV O BUF U10 DIG0_PIO01 PLD1 B 8 U11 DIG1_PIO02 PLD3 Clk12MHz A 7 MSB Logic C U2 BTN1 C 0 OUT PLD4 A D U12 AND2 B Y Key = Space PLD2 MSBA MSBB MSBC MSBD LSBA LSBB LSBC LSBD Clock A B C D E F G SEGA_PIO09 SEGB_PIO08 SEGD_PIO06 Copy of MUX Logic NextButton A ResetButton B C D D SEGC_PIO07 SEGE_PIO05 SEGF_PIO04 E LSB Logic E SEGG_PIO03 U1 BTN0 A Y B F F AND2 U3 1 200Hz G G 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 U5 A B A Y MUX2_1 B MSBA U1 C Y A MSBD ~LT ~RBI ~BI/RBO U3 OUT 1 A B Y A U8 A B A B C D LSBC ~LT ~RBI ~BI/RBO LSBD U4 F Y A OA OB OC OD OE OF OG A B INV A ~A/B ~G A B Y U19 ~A/B ~G Y MUX2_1 Y G ~A/B ~G OUT 0 DIGITAL_LOW 2 A F INV U11 U12 Y INV U10 MUX2_1 A B E U18 Y DIGITAL_HIGH 1 Y U9 OUT 1 0 D U17 MUX2_1 DEC_BCD_7 G Y INV ~A/B ~G E C U16 D LSBB Y INV MUX2_1 U2 B U15 A DIGITAL_HIGH LSBA F G ~A/B ~G DEC_BCD_7 A E Y INV MUX2_1 U7 OA OB OC OD OE OF OG INV C U14 ~A/B ~G A B C D B D U6 A B MSBC Y A ~A/B ~G MSBB A U13 Clock MUX2_1 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 A A U1 B INA INB R01 R02 DIGITAL_HIGH ResetButton QA QB QC QD B C U6 INV Y A CNTR_4BIN_AS A U2 OUT 1 A U4 C Y A Y U3 D D U7 INV C U5 B NAND2 A B Y NextButton D C B A NAND4 Y D INV E E F F G G 0 1 2 3 4 5 6 7 8 0 A 1 2 3 4 5 6 7 8 A U5 A B OUT 1 NextButton DIGITAL_HIGH C D B U2 U3 U4 U9 INV Y U1 A B ~PR D ~PR Q D ~PR Q D ~PR Q D Q C C CLK ~Q CLK ~CLR ~Q CLK ~CLR ~Q CLK ~CLR FF_D_PCLR_CO FF_D_PCLR_CO ~Q ~CLR FF_D_PCLR_CO FF_D_PCLR_CO U8 D ResetButton U6 Y Y B A B A NAND4 AND2 E D D C E Y A INV Y U7 A U10 INV F F G G 0 1 2 3 4 5 6 7 8