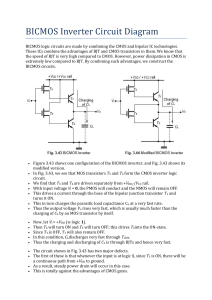

CHAPTER 15 CMOS DIGITAL LOGIC CIRCUITS Chapter Outline 15.1 CMOS Logic-Gate Circuits 15.2 Digital Logic Inverters 15.3 The CMOS Inverter 15.4 Dynamic Operation of the CMOS Inverter 15.5 Transistor Sizing 15.6 Power Dissipation NTUEE Electronics III 15-1 15.1 CMOS Logic-Gate Circuits Switch-Level Transistor Model NMOS and PMOS transistors as switches Switch on: small resistance Ron or rDS Switch off: open circuit The CMOS Inverter Invert the logic value of the input Represented by Boolean expression Y X When X = 1 (VX = VDD) Y = 0 (VY = 0V) When X = 0 (VX = 0V) Y = 1 (VY = VDD) NTUEE Electronics III 15-2 General Structure of CMOS Logic NMOS pull-down network (PDN) and PMOS pull-up network (PUN) operated by input variables in a complementary fashion Alternative Circuit Symbols for MOSFETS in Digital Circuits NTUEE Electronics III 15-3 Two-Input Logic Gates Two-input NOR gate, two-input NAND gate and Exclusive-OR gate NOR gate NAND gate NTUEE Electronics III XOR gate 15-4 Synthesis Method for PUN and PDN The PDN can be directly synthesized by expressing the inverted Boolean function in uncomplemented variables (inverters are needed if complemented variables appear in the expression) The PUN can be directly synthesized by expressing the nonverted Boolean function in complemented variables (inverters are needed if uncomplemented variables appear in the expression) The PUN can be also obtained from the PDN (and vice versa) using the duality property NTUEE Electronics III 15-5 Examples for CMOS Logic Gates Y AB Y AB AB Y A( B CD ) Y A B NTUEE Electronics III 15-6 15.2 Digital Logic Inverters The Voltage-Transfer Characteristic (VTC) The function of the inverter is to invert the logic value of its input signal The voltage-transfer characteristic is used to evaluate the quality of inverter operation VTC parameters VOH: output high level VOL: output low level VIH: the minimum value of input interpreted by the inverter as a logic 1 VIL: the maximum value of input interpreted by the inverter as a logic 0 Transition region: input level between VIL and VIH NTUEE Electronics III 15-7 Noise Margins The VTC is generally non-linear VIH and VIL are defined as the points at which the slope of the VTC is -1 Robustness (noise margin at a high level): NMH = VOHVIH Robustness (noise margin at a low level): NML = VILVOL Static inverter characteristics for ideal VTC: VOH = VDD VOL = 0 VIH = VIL = VDD/2 NMH = NML = VDD/2 Ideal VTC NTUEE Electronics III 15-8 Propagation Delay tPHL : high-to-low propagation delay tPLH : low-to-high propagation delay tP (propagation delay) = (tPLH+tPHL)/2 Maximum switching frequency fmax = 1/2tP The output transient of the inverter can be characterized by a RC charge/discharge model vO (t ) V (V V0 )e t / RC NTUEE Electronics III 15-9 Inverter Implementation Simplest implementation of the inverter with a MOSFET and a load Inverter implementation with complementary switches Inverter implementation with a double-throw switch NTUEE Electronics III 15-10 15.3 The CMOS Inverter Circuit Operation A CMOS inverter consists of an n-channel and a p-channel MOSFET The n-channel device turns on and the p-channel device turns off as the input level goes high The p-channel device turns on and the n-channel device turns off as the input level goes low 1 1 The turn-on device is modeled by a resistance: rDSN kn' W / L n (VDD Vtn ) and rDSP k p' W / L p (VDD | Vtp |) VOH = VDD and VOL = 0 for any CMOS inverter NTUEE Electronics III 15-11 The transistors go through five different operation regions as the input goes from 0 to VDD Region I: (QN off; QP tri.) iDN ( 0) iDP Region II: (QN sat.; QP tri.) iDN Region III: (QN sat; QP sat) iDN Region IV: (QN tri.; QP sat.) iDN Region V: (QN tri.; QP off) iDN Region I 1 1 kn (vI Vtn ) 2 iDP k p (VDD vI | Vtp |)(VDD vO ) (VDD vO ) 2 2 2 1 1 kn (vI Vtn ) 2 iDP k p (VDD vI | Vtp |) 2 2 2 1 1 k n (vI Vtn )vO vO2 iDP k p (VDD vI | Vtp |) 2 2 2 iDP ( 0) Region II Region IV Region III Region V NTUEE Electronics III 15-12 Static Characteristics of the CMOS Inverter Ratioless logic: VOH and VOL are independent of ratio of the transistors VOH = VDD VOL = 0 Static power dissipation is zero for both states Noise margins can be determined by the VTC The switching voltage (when vI = vO) is defined by VM r (VDD | Vtp |) Vtn r 1 where r kp kn p (W / L) p n (W / L) n VM increases with r (not a strong function) NML increases and NMH decreases as r increases NML decreases and NMH increases as r decreases NTUEE Electronics III 15-13 The Matched Inverter A matched inverter has equivalent pull-up and pull-down device with kn = kp and Vtn = |Vtp| = Vt The VTC is symmetric Determine VIL from the VTC in Region II: 1 1 (vI Vt ) 2 (VDD vI Vt )(VDD vO ) (VDD vO ) 2 2 2 vI Vt (VDD vO ) (VDD vI Vt ) dvO dv (VDD vO ) O dvI dvI 1 VIL (3VDD 2Vt ) 8 Determine VIH from the VTC in Region IV: 1 1 (vI Vt )vo vO2 (VDD vI Vt ) 2 2 2 dv dv vO (vI Vt ) O vO O (VDD vI Vt ) dvI dvI 1 VIH (5VDD 2Vt ) 8 Noise margins: NMH = NML = (3VDD+2Vt)/8 Switching voltage: VM = VDD/2 NTUEE Electronics III 15-14 15.4 Dynamic Operation of the CMOS Inverter Determining the Propagation Delay Evaluated by charging/discharge the output capacitor C through QP and QN Average current method: tPHL: 1 iDN ( E ) iDN (M ) 2 1 iDN ( E ) k n (VDD Vtn ) 2 2 2 VDD 1 VDD iDN ( M ) kn (VDD Vtn ) 2 2 2 CVDD C t PHL n 2 I av knVDD I av 7 3Vtn Vtn2 2 4 V VDD DD where n 2 / tPLH: t PLH C CVDD p 2 I av k pVDD 7 3 | Vtp | Vtp2 2 where p 2 / VDD 4 VDD Propagation delay: tP = (tPHL+tPLH)/2 NTUEE Electronics III 15-15 An alternative approach: Modeling the turn-on device as a resistance Use RC charge/discharge behavior to evaluate the propagation delay The empirical values of the resistors are given by RN 12.5 (k) (W / L) n and RP 30 (k) (W / L) p tPHL= 0.69RNC and tPLH= 0.69RPC Step function at input may underestimate propagation delay tPHL RNC and tPLH RPC NTUEE Electronics III 15-16 Determining the Equivalent Load Capacitance Components accountable for the equivalent load capacitance Transistor parasitic capacitances from Q1 and Q2 (intrinsic component) Input capacitance of the following stages (extrinsic component) Wiring capacitance or interconnect capacitance (extrinsic component) C ( 2C gd 1 2C gd 2 Cdb1 Cdb 2 ) (C g 3 C g 4 Cw ) Cint Cext NTUEE Electronics III 15-17 15.5 Transistor Sizing Inverter Sizing Minimum length permitted by the technology is usually used as the length for all channels Device aspect ratio (W/L)n is usually selected in the range 1 to 1.5 The selection of (W/L)p is relative to (W/L)n Matched inverter by (W/L)p : (W/L)n = n: p (W/L)p = (W/L)n: minimum area, small propagation delay (W/L)p = 2(W/L)n: a frequently used compromise Transistor sizing (aspect ratios are increased by a factor of S) versus propagation delay Load capacitance: C Cint Cext SCint 0 Cext Req 0 1 RN RP ) 2 S S S Equivalent resistance: Req ( Req 0 1 ( SCint 0 Cext ) 0.69 Req 0Cint 0 Req 0Cext S S Propagation delay: t P 0.69 The propagation decreases as S increases for cases where Cext dominates The propagation is nearly independent of the transistor sizing (S) for cases where Cint dominates NTUEE Electronics III 15-18 Transistor Sizing The (W/L) ratios are chosen for a worst-case gate delay equal to that of the basic inverter (assuming C is constant) The derivation of equivalent (W/L) ratio is based on the equivalent resistance of the transistors rDS (W / L) 1 1 1 Series Connection (W / L) eq ... (W / L)1 (W / L) 2 1 Parallel Connection (W / L) eq (W / L)1 (W / L) 2 ... Effects of Fan-In and Fan-Out Each additional input to a CMOS gate requires two additional transistors Increases the chip area and the propagation delay due to excess capacitive loading The number of NAND gate is typically limited to 4 Redesign the logic design may be required for a higher number of inputs Advantages of using CMOS logic: static power dissipation, ratioless design, noise margin Disadvantage of using CMOS logic: area, complexity, capacitive loading, propagation delay NTUEE Electronics III 15-19 Driving a Large Capacitance A large capacitive load drastically increases the propagation delay Use a large inverter to drive the load could alleviate the propagation delay The input capacitance increases accordingly equivalently shifting the burden forward Chain of scaled inverters in cascade to alleviate the problem with large capacitive load NTUEE Electronics III 15-20 15. 6 Power Dissipation Power Dissipation Static power dissipation: power dissipated when the inverter stays in logic 0 or logic 1 Dynamic power dissipation: power dissipated as the output is switching 0.5C(VDD)2 is dissipated in the PUN in each cycle 0.5C(VDD)2 is dissipated in the PDN in each cycle Dynamic power dissipation: PD = f C(VDD)2 Another component of power dissipation during switching results from the current conduction through QP and QN and the peak current for a matched inverter is given by I peak 1 V k n DD Vtn 2 2 2 Power-Delay Product and Energy-Delay Product Power and delay are often in conflict for inverter operation Power-delay product is a figure-of-merit for comparing logic-circuit technologies or families 2 /2 Power-delay product is defined as PDP PDt P CVDD 2 tP / 2 Energy-delay product (energy per transition) is defined as EDP CVDD NTUEE Electronics III 15-21