Notes on Unit-2

Hardware Description Language (HDL)

•

A hardware description language (HDL) is used to describe the structure and behavior

of digital electronic circuits.

•

A hardware description language allows for the automated analysis and simulation of

an electronic circuit.

•

It allows the synthesis of an HDL description into a netlist, which can then be routed to

produce the set of masks used to create an integrated circuit.

•

A hardware description language is like a programming language such as C

•

Two HDL are there:

Verilog & VHDL

Basic VLSI Design flow

Synthesis Tools

In a fully automated design, the RTL description is sent though the synthesis tool that

produces a netlist of the hardware components needed to build the system.

High speed, Low power, Low area requirement can be optimized.

Synthesis Tools

FPGA - Field Programmable Gate Array.

ASIC - Application Specific Integrated Circuit.

Basics of Verilog

0

: zero

1

: one

X,x :- unknown

Z,z :– High impedance state (open circuit)

Number Representation in Verilog

<size>’<radix><value>

size- No. of bits

radix – b (Binary), o (Octal), d (Decimal), h (Hexadecimal)

value – 0, 1 (Binary)

0 – 7 (Octal)

0 – 9 (Decimal)

0 – 9, A, B, C, D, E, F (Hexadecimal)

Ex1 : 4’b1010

Ex2: 8’hAX = 1010xxxx

Ex3 : 12’o3zx7 = 011zzzxxx111

Ex4 : 8’hA9 = 10101001

Ex5 : 16’hF1 = 0000000011110001

Ex6 : 10’o6x2 = 0110xxx010

Ex7 : 8’b1 = 00000001

Conditional Operator

•

cond_expr ? true_expr : false_expr

2 x 1 MUX

Data Types

Port Declaration

Input port (input)

Output port (output)

Bidirectional port (inout)

Scalar declaration

input A,B,C_in;

output x,y z;

Vector declaration

input [15:0]A,B,data_in;

output [7:0]x,y, data_out;

Modules

A module is the basic building block in Verilog

Elements are grouped into modules to provide common functionality that is used at

many places in the design

A module provides the necessary functionality to the higher-level block through its

port interface (inputs and outputs), but hides the internal implementation.

Modules can not be nested

in1 my_module

in2

out1

out2

inN

outM

f

module my_module(out1, .., inN);

output out1, .., outM;

input in1, .., inN;

.. // declarations

.. // description of f

endmodule

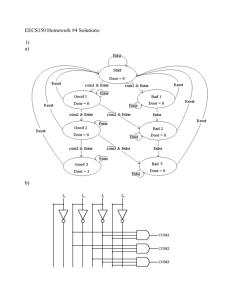

Event Control

Edge Triggered Event Control

@ (posedge clk)

// at positive edge of clk

Curr_state = next_state

or

@ (negedge clk)

// at negative edge of clk

Curr_state = !next_state

Level Triggered Event Control

@ (A or B)

// change in values of A or B

out = A&B;

Types of Verilog Coding

Assignment

Gate level modelling

Verilog code(Structural Modelling) for 3-bit squarer circuit

Verilog code of Half-adder

Verilog code of Full-adder

Verilog code of 4-bit Ripple Carry Adder

Verilog code of 4-bit Ripple Carry Adder/Subtractor

module 4bit_AS(C4,S,A,B,AS);

output C4;

output [3:0]S;

input AS;

input [3:0]A,B;

wire M,N,C5;

wire [3:0]R,P,Q,G;

and G1(G[0],A1,0);

and G2(G[1],A1,0);

and G3(G[2],A1,0);

and G4(G[3],A1,0);

xor G5(R[0],B[0],AS);

xor G6(R[1],B[1],AS);

xor G7(R[2],B[2],AS);

xor G8(R[3],B[3],AS);

4bit_RCA M1(C4,P,A,R,AS);

not G9(M,C4);

and G10(N,M,AS);

xor G11(Q[0],P[0],N);

xor G12(Q[1],P[1],N);

xor G13(Q[2],P[2],N);

xor G14(Q[3],P[3],N);

4bit_RCA M2(C5,S,G,Q,N);

endmodule

Design of 2 x 2 multiplier

Design of 3 x 4 multiplier

Verilog code of a 3 x 4 multiplier

module 3x4_Multiplier(C6,S,A,B);

output C6;

output [5:0]S;

input [2:0]A,[3:0]B;

wire [11:1]w;

wire [3:0]p;

wire C4,Cin,x;

and G1(Cin,A[1],0);

and G2(x,A[1],0);

and G3(S[0],A[0],B[0]);

and G4(w[1],A[0],B[1]);

and G5(w[2],A[0],B[2]);

and G6(w[3],A[0],B[3]);

and (w[4],A[1],B[0]);

and (w[5],A[1],B[1]);

and (w[6],A[1],B[2]);

and (w[7],A[1],B[3]);

and (w[8],A[2],B[0]);

and (w[9],A[2],B[1]);

and (w[10],A[2],B[2]);

and (w[11],A[2],B[3]);

4bit_RCA M1(C4,p,w[7:4],x,w[3:1],Cin);

buf(S[1],p[0]);

4bit_RCA M2(C6,S[5:2],w[11:8],C4,p[3:1],Cin);

endmodule

Verilog code of 1 bit comparator

Verilog code of 2 bits comparator

Verilog code of 4 bits comparator

Design of 8 x 3 Encoder

Verilog code for 8 x 3 Encoder

module 8x3_Encoder(z,x);

output [2:0]z;

input [7:0]x;

or G1(z[0],x[1],x[3],x[5],x[7]);

or G2(z[1],x[2],x[3],x[6],x[7]);

or G3(z[2],x[4],x[5],x[6],x[7]);

endmodule

Design of 4 x 2 Priority Encoder

Design of 2 x 4 Decoder

Verilog code for 2 x 4 Decoder

Verilog code for 2 x 4 Decoder with enable input

Verilog code for 3 x 8 Decoder

Multiplexer

Verilog code for 2x1 multiplexer

Verilog code for 4x1 multiplexer using 2x1 multiplexers

Verilog code for 8x1 multiplexer using 4x1 and 2x1 multiplexers

Demultiplexer

Verilog code for 1x2 Demultiplexer

Verilog code for 1x4 demultiplexer using 1x2 demultiplexers

Verilog code for 1x8 demultiplexer using 1x4 and 1x2 demultiplexers

Verilog code for S’R’ Flip-flop

Verilog code for SR Flip-flop

Verilog code for clocked SR Flip-flop(positive level triggered)

Verilog code for clocked D Flip-flop(positive level triggered)

Verilog code for clocked JK Flip-flop(positive level triggered)

Verilog code for clocked T Flip-flop(positive level triggered)

Verilog code for Master-slave Flip-flop(negative edge triggered)

Basics of dataflow modelling

•

•

•

Dataflow modeling makes use of the functions that define the working of the circuit

instead of its gate structure.

Dataflow modeling has become a popular design approach, as logic synthesis tools

became sophisticated.

This approach allows the designer to focus on optimizing the circuit in terms of the

flow of data.

Dataflow modeling uses several operators that act on operands to produce the desired

results.

Verilog provides about 30 operator types.

Symbol

Operation

+

Binary Addition

-

Binary Subtraction

&

Bitwise AND

|

Bitwise OR

^

Bitwise XOR

~

Bitwise NOT

==

Equality

>

Greater than

<

Less than

{}

Concatenation

?:

Conditional

Continuous Assignments

Dataflow modeling describes hardware in terms of the flow of data from input to output.

The dataflow modeling style is mainly used to describe combinational circuits. The primary

mechanism used is a continuous assignment.

A value is assigned to a data type called net, which is used to represent a physical connection

between circuit elements in a continuous assignment.

The value assigned to the net is specified by an expression that uses operands and operators.

A continuous assignment statement starts with the keyword assign.

Syntax

The syntax of a continuous assignment is

assign [delay] LHS_net = RHS_expression;

•

Continuous statements are always active statements, which means that if any value

on the RHS changes, LHS changes automatically after the delay unit.

Example

assign out1 = in1 & in2; // perform and function on in1 and in2 and assign the result to out1

assign #5 out2 = in1 & in2;

// perform and function on in1 and in2 and assign the result to out1 after a delay

Examples of dataflow modelling

Look-ahead Carry Adder

Propagation Delay

Physical logic gates have a propagation delay between the time that an input changes and the

time that the output responds to the change. The primitives in Verilog have a default delay of

0, meaning that the output responds to the input immediately.

module 2x2_Multiplier(C3,S,A,B);

output C3;

output [2:0]S;

input [1:0]A,B;

wire [4:1]w;

and #1 G1(S[0],A[0],B[0]);

and #1 G2(w[1],A[0],B[1]);

and #1 G3(w[2],A[1],B[0]);

and #1 G4(w[3],A[1],B[1]);

HA M1(w[4],S[1],w[1],w[2]);

HA M2(C3,S[2],w[3],w[4]);

endmodule

Introduction to Vivado Tool

f

Test Bench Code

Verilog test benches are used for the verification of the digital hardware design. Verification

is required to ensure the design meets the timing and functionality requirements.

Verilog Test benches are used to simulate and analyze designs without the need for any

physical hardware or any hardware device. The most significant advantage of this is that you

can inspect every signal /variable (reg, wire in Verilog) in the design.

In the Verilog testbench, all the inputs become reg and output a wire. The Testbench simply

instantiates the design under test (DUT). It applies a series of inputs. The outputs should be

observed and compared by using a simulator program.

Test Bench Code for half-adder

module half_adder_tb();

reg t_a, t_b;

wire SUM, CARRY;

half_adder dut(.a(t_a),.b(t_b),.sum(SUM),.carry(CARRY));

initial begin

t_a=0;t_b=0;

#10

t_a=0;t_b=1;

#10

t_a=1;t_b=0;

#10

t_a=1;t_b=1;

#10

$stop;

end

endmodule

Simulation Result