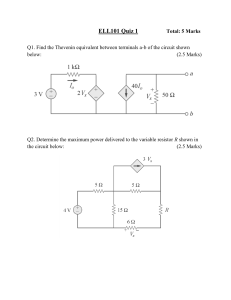

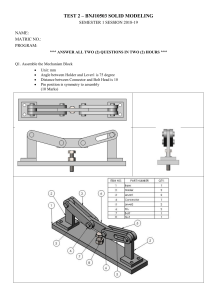

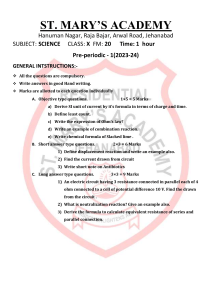

National Institute of Technology, Mizoram Mid – Semester Examination 2021 Digital Logic Design (ECL 1302) 3rd Semester (ECE, EEE, CSE) Full Marks: 15 marks Duration: 1:00 hour Answer all questions 1. (a) Implement the expression using a 16:1 Multiplexer. f (A,B,C,D) = ∑ m (0,2,3,6,8,9,12,14) (5) (b) Implement the Boolean expression and logic diagram of Full Subtractor using only NAND gates. (5) (d) For the logic circuit shown in the figure 1 below, the output Y is equal to (A) ABC (B) A + B + C (C) AB + BC + A + C (D) AB + BC (2.5) Figure 1 (e) The switching circuit given in the figure 2 can be expressed in binary logic notation as (A) L = (A+B) (C+D) E (B) L = AB + CD + E (2.5) (C) L = E + (A+B) (C+D) (D) L = (AB+CD) E Figure 2