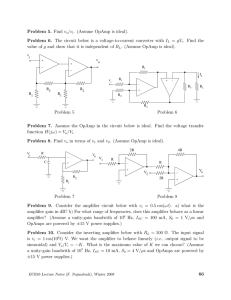

Low Power High Speed Operational Amplifier Design Using Cadence Ahsan Javed Awan and Peter Wilson Abstract—In this paper, the design space that optimizes the performance of operational amplifier in terms of current consumption and unity gain band width product has been explored using Cadence. A two stage indirect compensated active load cascode operational amplifier with a current consumption of 335uA and a speed as high as 23MHz has been presented. A novel indirect compensated multistage opamp designed in AMS 0.35um technology further reduces the current to 120uA and increases the speed to 35MHz. The layout of both designs incorporates Common Centroid method for improved matching among devices The most well known miller compensated operational amplifier with zero nulling resistor that fulfills the above captioned design goals has been discussed in Section II, Section III explains active load cascode topology as a first attempt toward the goal of low power and high speed design. Section IV unveils the multistage opamp topology using indirect compensation approach. Section V covers test circuitry used to determine the performance metrics and layout considerations. Simulation results are discussed in Section VI. Finally the concluding remarks are given in section VII. Keywords— Indirect Compensation, Low Power, Split Length Differential Pair, Three Stage Opamp. TABLE I DESIGN SPECIFICATIONS I. INTRODUCTION O perational Amplifiers are one of the basic components in integrated systems on chip that are designed to meet the stringent constraints of area, power and speed i.e. in a mobile phone 1W is available for the base band signal processing, so in order to coupe up the power limitation for the whole system, it is inevitable to design the individual building blocks with minimum current consumption. Moreover those key components should also be designed for higher speeds for higher throughput of the overall system. C.Zhang in [1] has designed an ultra low power (40uW) operational amplifier using a forward biased source substrate junction approach along with a low voltage current mirror but its performance degrades in terms of unity gain band width product and slew rate. Jirayuth in [2] and [3] has proposed operational amplifiers for less than 500uW power consumption but his designs too suffer from low gain band width product. Alfonso in [4] has discussed various design methodologies for low power operational amplifiers that include the use of telescopic opamp, but all of them have a limitation either on their open loop gain or unity gain bandwidth product. Hence in order to meet the minimum design specifications given in Table I, different design topologies are to be simulated and parametrically analyzed using Cadence tools. Ahsan Javed Awan was with the ECS Department, University of Southampton, SO171BJ, UK. He is now with 3W Systems (Pvt) Ltd Rawalpindi, 46000, Pakistan (corresponding author phone: 0092-3335315137; e-mail: ahsanjaved_nust@ yahoo.com) Peter Wilson is with the ECS Department, University of Southampton, SO171BJ, UK (email: pwr@ecs.soton.ac.uk) Parameter Open Loop Gain (db) Phase Margin (degrees) Gain BandWidth Product (MHz) Idd (µA) Slew Rate (V/µs) Load (pF) VDD (V) VSS (V) Value > 80 > 50 >150 < 350 > 20 10 1.67 -1.67 II. MILLER COMPENSATED OPAMP WITH ZERO NULLING RESISTOR In order to design miller compensated opamp for greater than 80dB gain, both PMOS and NMOS transistors are connected in diode configuration and biased using 10uA current source, The widths are adjusted so that Vdsat of both the transistors becomes equal to 5% of Vdd. So 11.5u for PMOS and 2.6u for NMOS results in the required Vdsat. The transconductance of each transistor is simulated for various lengths and the optimum one turns out to be 0.8um. A simple beta multiplier [5] is designed using the above transistor lengths and widths. This opamp design comprises of NMOS differential stage and Class A output stage. Using parametric analysis the optimum number of fingers for the differential pair is obtained. The value of miller capacitor and number of fingers in the output stage are adjusted to trade off between slew rate and phase margin. The schematic is shown in Fig. 1. The transistor sizes are tabulated in Table II and the simulation results are given in Table III. III. INDIRECT COMPENSATED ACTIVE LOAD CASCODE OPAMP Vishal and Jacob Baker in [6] have discussed various indirect compensated two stage topologies and have established a theory of indirect feedback compensation. Active load cascode topology from their paper has been used as a starting point (see Fig. 2). In fact the active load of the opamp designed in section I is cascoded, this generates a low impedance node between two active loads and feedback current is fed through this node. This also eliminates the need of zero nulling resistor. consumption. Table IV gives the transistor sizes for this topology. The design is simulated and post layout model with parasitic capacitances is also simulated and results are presented in Table V. Fig. 1 Miller Compensated Opamp with Biasing Circuitry TABLE II TRANSISTOR SIZES OF MILLER COMPENSATED OPAMP Transistor Label Mb1 Mb2 Mb3 Mb4 Mb5 Mb6 M1 M2 M3 M4 M5 M6 M7 Total Width(Wtot) in µm 11.4 11.4 2.6 2.6 10.4 2.6 34.2 34.2 13 13 15.6 285 65 No of Gates(ng) 2 2 2 2 8 2 6 6 10 10 12 50 50 TABLE III PERFORMANCE SUMMARY OF MILLER COMPENSATED OPAMP Performance Metric Open Loop Gain (db) Phase Margin (degrees) Gain BandWidth Product (MHz) Idd (µA) Slew Rate on Rising Edge (V/µs) Slew Rate on Falling Edge (V/µs) Power Dissipation (mW) Post Schematic 81 57 28 346 41 20 1.4 The biasing circuitry is the same used in Miller Compensated Opamp. The parameters are again tweaked to not only meet the design criteria but also to reduce the current Fig. 2 Indirect Compensated Active Load Cascode Opamp. TABLE IV TRANSISTOR SIZES OF INDIRECT COMPENSATED ACTIVE LOAD CASCODE OPAMP Transistor Label M1 M2 M1a M2a M3 M4 M5 M6 M7 Total Width(Wtot) in µm 28.5 28.5 28.5 28.5 2.6 2.6 10.4 318.6 72 No of Gates(ng) 2 2 2 2 2 2 8 36 36 TABLE V PERFORMANCE SUMMARY OF INDIRECT COMPENSATED OPAMP Performance Metric Open Loop Gain (db) Phase Margin (degrees) Gain BandWidth Product (MHz) Idd (µA) Slew Rate on Rising Edge (V/µs) Slew Rate on Falling Edge (V/µs) Power Dissipation (mW) Post Schematic 91 61 23 334 27 22 1.1 Post Layout 91 61 22 335 26 21 1.1 IV. INDIRECT COMPENSATED THREE STAGE OPAMP In a two stage opamp design, there is a limitation of slew rate because it mainly depends on the current in the output stage and the load capacitance. So for a slew rate of 20V/us the current consumption can’t be reduced beyond a 300uA.To mitigate the problem of slew rate Class AB output buffer stage can be incorporated in the design. The realization of Class AB buffer stage using floating current source to bias the push pull output stage requires additional circuitry to bias that current source which adds to the area overhead. So Class AB stage has been realized by cross connecting the two NMOS differential stages and driving the PMOS of common source output stage with output of first differential stage as presented in [7]. Fig. 3 explains these connections. requirements. The gain beyond 80db is achieved by increasing the widths of split length differential pairs. Table VI gives the transistor sizes obtained as the result of iterative simulations and the performance of designed topology is expressed in TABLE VII. TABLE VII PERFORMANCE SUMMARY OF IDIRECT COMPENSATED THREE STAGE OPAMP STAGE Performance Metric Open Loop Gain (db) Phase Margin (degrees) Gain BandWidth Product (MHz) Idd (µA) Slew Rate on Rising Edge (V/µs) Slew Rate on Falling Edge (V/µs) Power Dissipation (mW) Post Schematic 83 80 35 120 50 25 .396 Post Layout 83 76 35 122 50 23 .402 V. TESTING AND LAYOUT Fig. 3 Indirect Compensated Split Length Differential Pair Opamp with Class AB Output Stag TABLE VI TRANSISTOR SIZES OF INDIRECT COMPENSATED THREE STAGE OPAMP Transistor Label M1 M2 M3a M3b M4a M4b M5 M6 M7 M8 M9 M10 M11 M12 Total Width(Wtot) in µm 11.4 11.4 20.8 20.8 20.8 20.8 10.4 11.4 11.4 2.8 2.8 5.2 11.4 2.6 No of Gates(ng) 2 2 2 2 2 2 8 2 2 2 2 10 2 2 The low impedance node is created using the split length differential pair in the first stage. The effect of a split length transistor can be achieved by using two common gate transistors each with twice the width of original one [8]. The limitation of slew rate in Class AB output stage comes from the biasing current through the differential pair and the compensation capacitance between the first two stages. Hence to achieve a higher slew rate, this minimum value of this compensation capacitance is chosen i.e. 300fF.This brings in a need of a resistor in series to meet the phase margin In order to find out the frequency response of the proposed designs, load capacitance is attached at the output and 100MOhm resistor is used in the feedback path of inverting input which is then grounded via large capacitor of 100uF.This provide a path to any feedback signal to ground at higher frequencies. The non inverting input is fed through dc source with ac magnitude of 1V and dc voltage 0V since the common mode input voltage is almost zero for all the above proposed designs. For slew rate and total current measurement, opamp is connected in unity gain buffer configuration with load capacitance at the output and +/500mV pulse of period 2us is applied at the non inverting input and transient analysis is made. Current measurement is made at the Vdda node of the opamp and its average gives the total current consumption. The overview of testing circuitry to conduct post schematic and post layout simulations is shown in Fig. 4. Fig. 4 Testing Circuitry The layout of designs discussed in section II and III has been created using the common centroid method and are shown in Fig. 5(a) and Fig. 5(b) respectively. For simplification purposes ABBA pattern has been used for the transistors in the all PMOS active loads, in all differential pairs and in the NMOS stage of beta multiplier. This means that all those transistors which were earlier designed as finger multiples of basic NMOS and PMOS transistors biased with 10uA current have to be split into two transistors. For that the width strips in the original schematic are modified for two fingers in order to keep the overall widths same as before. Hence the layout specific schematic replaces the original transistors with two transistors connected in parallel. This also affects the biasing of transistors too so the resistance in the beta multiplier needs to be readjusted. The DRC errors have been checked by using no_coverage switch. The layout is then extracted with parasitic and post layout simulation is performed to see the effects of parasitic capacitances on the performance of presented opamps does not have a zero slope, it affects the performance of designs proposed against the voltage variations, The analogue extracted form of designs are tested for the worst case i.e. the supply voltage of +/- 1.42V. Active Load Cascode opamp is affected only little with a reduction of 1db in gain, 1V in the slew rate. But the three stage opamp is largely affected by the supply voltage variations. The gain bandwidth product reduces by 10MHz and slew rate by 4V. The reason is that the current through the spit length differential pair reduces and since the compensation capacitance of 300pF is fixed, the slew rate drops. . Fig. 5(b) Layout of Indirect Compensated Three Stage Opamp VI. CONCLUSION Fig. 5(a) Layout of Indirect Compensated Active Load Opamp The layout area for active load cascade opamp, calculated by the tool, is 7552 and area of indirect compensated split length differential pair opamp with class AB output stage is 5488 . Since the beta multiplier designed for the biasing The parasitic effects decreases the slew rate and unity gain bandwidth so it is better to add a safety margin of 5 to 10% on the original specifications in order to reduce the probability of iterating through the simulation phase again. Three designs have been presented all of which meet minimum design criteria and three stage opamp design provides an optimum solution for higher speed and low power consumption. Moreover it is also optimized with respect to area. Though the three stage opamp design meets the minimum design criteria even with 15% supply voltage variations, its robustness can be increased by the cascaded version of beta multiplier. The area in turn is still expected to be comparable with that of active cascade load opamp design. APPENDIX Fig. 6(a) Frequency Response of Miller Compensated Opamp Phase margin is 57deg at fun = 28MHz Fig. 6(b) Transient Response of Miller Compensated Opamp used as a Unity Gain Buffer Fig. 7(a) Frequency Response of Indirect Compensated Active Load Cascode Opamp. Phase margin is 61deg at fun = 22MHz Fig. 7(b) Transient Response of Indirect Compensated Active Load Cascode Opamp used as a Unity Gain Buffer REFERENCES [1] [2] [3] [4] [5] [6] [7] [8] Fig. 8(a) Frequency Response of Indirect Compensated Split Length Differential Pair Opamp with Class AB Output Stage. Phase margin is 75deg at fun = 35MHz Fig. 8(b) Transient Response of Indirect Compensated Split Length Differential Pair Opamp with Class AB Output Stage used as a Unity Gain Buffer ACKNOWLEDGMENT The Author thanks Dr. Li Ke, a Researcher at ECS Department for explaining the current based opamp design approach which has proved to be a starting point for all the three designs presented in this paper. C.Zhang, A.Srivastava and P.K.Ajmera, “A 0.8V Ultra Low Power CMOS Operational Amplifier Design”, IEEE 2002 45th Midwest Symposium on Circuits and Systems, Vol1, pp I-9-12, Aug2002. Jirayuth Mahattanakul, and Jamorn Chutichatuporn, “Design Procedure for Two-Stage CMOS OpampWith Flexible Noise-Power Balancing Scheme”, IEEE Transactions on Circuits and Systems-I, Vol.52, pp 1508-1514, August 2005. Jirayuth Mahattanakul, “Design Procedure for Two-Stage CMOS Operational Amplifiers Employing Current Buffer”, IEEE Transactions on Circuits and Systems-II, Vol.52, pp 766-770, August 2005. Alfonso Cesar B. Albason, Neil Michael L. Axalan, Maria Theresa A. Gusad,John Richard E. Hizon and Marc D. Rosales, “Design Methodologies for Low-Power CMOS Operational Amplifiers in a O.25um Digital CMOS Process” TENCON 2006, 2006 IEEE Region 10 Conference, pp 1-4, Nov 2006 David Johnes, Kennth W. Martin, Analogue Integrated Circuit design, John Wiley & Sons 1997. Vishal Saxena and R. Jacob Baker, “Indirect Feedback Compensation of CMOS Op-Amps”, IEEE Workshop on Microelectronics and Electron Devices 2006, Vol1, pp 3-4, Aug 2006. Vishal Saxena and R. Jacob Baker, “Indirect Compensation Techniques for Three-Stage CMOS Opamps”, 52st IEEE Midwest Symposium on Circuits and Systems, pp 9-12, Aug 2009. Vishal Saxena and R. Jacob Baker, “Compensation of CMOS Op-amps using Split-Length Transistors” 51st IEEE Midwest Symposium on Circuits and Systems, pp 109-112, Aug 2008.