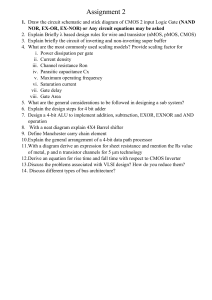

VLSI TECHNOLOGY A Summer training report Submitted in Partial Fulfillment of the Requirement of The Degree Of BACHELOR OF TECHNOLOGY In ELECTRONICS AND COMMUNICATION ENGINEERING Completed at PIE INFOCOMM PVT.LTD.LUCKNOW Duration 11 june to 25 july,2018 Submitted By GIRJESH VERMA (1574831003) Department of Electronics Engineering ANSAL TECHNICAL CAMPUS LUCKNOW (U.P.) INDIA-226030 ACKNOWLEGEMENT I have taken efforts in this summer training report. However, it would not have been possible without the kind support and help of many individuals and organizations. I would like to extend my sincere thanks to all of them. I am highly indebted to Mr.Nagendra Yadav Sir (HOD Electronics and Communication) for their guidance and constant supervision as well as for providing necessary information regarding the training. I would like to express my gratitude towards my parents & member of PIE INFOCOMM for their kind co-operation and encouragement which help me in completion of this project. I would like to express my special gratitude and thanks to industry persons for giving me such attention and time. My thanks and appreciations also go to my Batchmates in making the report and people who have willingly helped me out with their abilities. 1. INTRODUCTION TO VLSI CONTENT 2. VLSI DESIGN METHODOLOGY System specification and architecture design Logical design Functional design Fabrication Packaging 3. TOP DESIGN METHODOLOGY System level RTL Algorithmic Gate level Transistor(also called switch) level 4. DESIGN TRENDS IN VLSI 5. CHALLENGES IN VLSI TECHNOLOGY 6. CMOS FABRICATION PROCESS 7. DIGITAL FUNDAMENTALS Models associated Characterization for analog design Static dissipation Gate level simulation 8. CMOS CIRCUIT CHARACTERIZATION Power consumption Dynamic dissipation Analog CMOS Resistance estimation Temperature range Power consumption Dynamic dissipation Electronic data processing 9. CMOS logic gate design Combinational logic analysis AND-OR Logic: Basic Combinational Logic Circuits AND-OR Invert Logic: Exclusive-NOR Logic: Exclusive-OR Logic: Universal Gates 10. DYNAMIC CMOS LOGIC 11. STATIC VERSUS DYNAMIC LOGIC 12. SEQUENTIAL LOGIC SHIFT REGISTER- SERIAL DATA TO PARALLEL DATA LATCH SHIFT REGISTER- SERIAL DATA TO PARALLEL BINARY UP COUNTER BINARY DOWN COUNTER 13. MEMORIES MEMORY STRUCTURE TYPES OF MEMORY MEMORY MAPPING MEMORY ORGANISATION 14. TYPES OF SEMICONDUCTOR MEMORY TECHNOLOGIES PROM FLASH MEMORY EEPROM NOR FLASH NAND FLASH 15. ANALOG DESIGN Analog ciruit Reverse bias P-N JUNCTION NPN Forward bias junction NPN reverse bias junction Relation between alpha and beta 16. Small signal analysis 17. VLSI DESIGN METHODOLOGY Introduction LEVELS OF REPRESENTATION AND DESIGN: DESIGN FLOW BUILDING: COMPLEXITY AND DESIGN: 18. SCHEMATIC SIMULATION SOFTWARE INTRODUCTION: MOS SIMULATIONS: METAL OXIDE SEMICONDUCTOR FIELD EFFECT THANSISTOR: 19. Ic layout LAYOUT RULES: 20. CONCLUSION 21. FUTURE SCOPE INTRODUCTION TO VLSI Integrated Circuits are tiny electronic circuit used to perform a specific electronic function, such as amplification. The first integrated Circuit (IC) was invented by Jack Kilby in 1958. As suggested by Moore, the capacity doubled roughly every 18 month. Today, a large single VLSI chip can contain over one billion transistors. These days, VLSI chiefly comprises of Front End Design and Back End design. Front end design includes digital design using HDL and design verification through simulation and other techniques. The backend design comprises of CMOS library design and its characterization. It also covers the physical design and fault simulation. VLSI DESIGN METHODOLOGIES The design methodology implies the complete process of creating a VLSI design. Following steps shows various steps involved in creating a VLSI design from Concept to the Final product. Fig: VLSI DESIGN METHODOLOGY SYSTEM SPECIFICATION AND ARCHITECTURAL DESIGN VLSI design cycle start with a formal specification of a VLSI chip. At this stage, the system specifications are laid out. This involves a high level representation of the system. FUNCTION DESIGN In this stage, main functional units of the system and the interconnect requirements between the units are identified. The main purpose of this stage is to specify system behavior, in terms of Input, Output, and Timing of each unit. The outcome of functional design is usually a diagram showing relationship of time and other aspects between units. LOGIC DESIGN In this stage, the logic for the VLSI system is designed. This includes, Boolean expressions, control flow, word width, register allocation, etc. The outcome of this stage is Register Transfer Level (RTL) description. RTL is expressed in a Hardware Description Language (HDL) like VHDL and Verilog. CIRCUIT DESIGN The purpose of the circuit design is to develop a circuit representation based on the logic design. The outcome of this stage is a netlist. Netlist is an electronic circuit system consisting of all of the circuit element names/reference designators, listed in a format with their input and output signal names. FABRICATION Fabrication process includes lithography, polishing, deposition, diffusion, etc. This process consists of several steps and requires various masks. Before the chip is mass produced, a prototype is made and tested. PACKAGING Packaging involves putting together the chips on a Printed Circuit Board (PCB) or a Multi-Chip Module(MCM). Top-Down design Methodology Fig: VLSI PACKAGING In this methodology, a complete system is described at an abstract level using hardware description language (HDL) and the use of EDA tools like partitioners and synthesizers. SYSTEM LEVEL All the inputs and outputs are described at this level. This level does not touch the hardware structure at all. It simply treats the design like a black box. ALGORITHMIC (BEHAVIORAL) LEVEL This is the highest level of abstraction provided by most HDLs. RTL (Register Transfer Level/ Dataflow) At this level the module is designed by specifying the data flow between the registers. GATE LEVEL The module is implemented in terms of logic gates and interconnections between these gates. Design at this level is similar to describing a design in terms of gate-level logic diagram. Transistor (also called Switch) Level This is the lowest level of abstraction. A module can be implemented in terms of switches, storage nodes, and the interconnections between them. CHALLENGES IN VLSI TECH. Shrinking geometries, lower power voltages, and higher frequencies of integrated circuits have a negative impact on reliability. All these factors increase the number of occurrences of intermittent and transient faults. The approach of fault avoidance and fault tolerance is used to increase the reliability of VLSI circuits. As technology scales, many new opportunities emerge for VLSI designers. Understanding technology trends and specific applications is the main criterion for designing efficient and effective chips. There are several difficult and exciting challenges facing the design of complex Integrated Circuits. To continue its phenomenal historical growth and continue to follow Moore’s law, the semiconductor industry will requires advances on all fronts. CMOS FABRICATION PROCESS Complementary Metal Oxide Semiconductors (CMOS) have been one of the main technologies for economic growth during the past half-century. These circuits have enabled the creation of many important products such as personal computer, cellular phones, global positioning systems, medical instruments as well as other applications. MOS TRANSISTOR The metal-oxide-semiconductor field-effect transistor (MOSFET or MOS, for short) is certainly the most dependable of the contemporary digital designs. Fig: MOSFET The voltage applied to the gate terminal determines if current should flow through the source and the drain ports and how much current flows between the source and the drain ports. At the surface level, the transistor can be considered to be a switch. The larger the voltages difference between gate and source the larger the current. NMOS TRANSISTOR NMOS Transistor consists of n+ drain and source regions, embedded in a p-type substrate. PMOS TRANSISTOR PMOS Transistor consists of p+ drain and source regions, embedded in a n-type substrate. In a complementary MOS technology (CMOS), both devices are present. The circuit symbols for the various MOS transistors are shown in the adjacent page. Fig: MOS TRANSISTORS OPERATING PRINCIPLE OF A MOSFET . Fig: I-V CHARACTERISTICS The MOSFET is a device where the voltage on the gate terminal controls the flow of current between the output terminals, Source and Drain. The source terminal is common between the input and the output of a MOSFET. The output characteristics of a MOSFET are then a plot of drain current (iD) as a function of the Drain —Source voltage (Vds) with gate source voltage (Vgs) as a parameter. Fig. operation of MOSFET THE CMOS TECHNOLOGY CMOS Stands for "Complementary Metal Oxide Semiconductor." This technology is used in making transistors. The CMOS-based transistors either positive or negative charge, they run efficiently, using up very little power. Due to this efficiency, processors that use CMOS-based transistors can run at extremely high speeds without getting too hot. OXIDATION Oxidation is the process by which a layer of silicon is grown on the surface of a silicon wafer. DIFFUSION Diffusion is the movement of impurity atoms at the surface of the silicon into the bulk of the silicon. ION IMPLANTATION Ion implantation is the process by which impurity ions are accelerated to a high velocity and physically lodged into the target material DEPOSITION Deposition is the means by which various materials are deposited on the silicon wafer. The deposition is typically made through a chemical-vapour deposition (CVD). ETCHING Etching is the process of selectively removing a layer of material. When etching is performed, the etchant may remove portions or all of:- The desired material; The underlying layer; The masking layer. EPITAXY Epitaxy growth consist of the formation of a layer of a single silicon on the surface of the silicon material across the interface. CMOS PROCESS STEPS Step 1 – Implantation and diffusion of the n-wells. Step 2 – Growth of thin oxide and deposition of Silicon nitride. Step 3 – Selective removal of the silicon nitride. Step 4 – Growth of the thick field oxide (LOCOS –localized oxidation of silicon). Step 5 – Removal of the nitride, growth of the thin gate oxide and deposition of polysilicon. Step 6 – Selective removal of polysilicon. Step 7 – Implantation of the NMOS and PMOS (not shown) source and drain diffusion. Step 8 – Deposit a thick oxide layer (BPSG –borophosphosilicate glass). Step 9 – Open contacts. Step 10 –Deposit first level metal. Step 11 –Etching unwanted metal and passivation. CMOS INVERTER The circuit diagram of the CMOS inverter is shown in figure (4). ADVANTAGES OF CMOS INVERTER • The voltage swing is the same as the supply voltage. • The size of the transistors can be minimized. •. The inverter can be designed to have a low input impedance, making it less sensitive to noise. DIGITAL FUNDAMENTAL There are two types of digital logic :- combinational logic and sequential logic. In practice both types of logic are used. BOOLEAN ALGEBRA True is represented by the value 1. False is represented by the value 0. Variables are represented by letters and can have one of the two values, either 0 or 1. Operations are functions of one or more variables. AND is represented by X.Y OR is represented by X+Y NOT is represented by X' OPERATIONS AND EXPRESSIONS Addition and multiplication are the basic operation in Boolean algebra. ADDITION MULTIPLICATION 0+0=0 0*0=0 0+1=1 1*0=0 1+0=1 1*0=0 1+1=1 1*1=1 Laws Of Boolean Algebra 1. Commutative law of addition : A+B=B+A 2. Associative Law Of Addition : A+(B+C)= (A+B)+C 3. Commutative Law Of multiplication : A*B=B*A 4. Associative Law of Multiplication : A(BC)=(AB)C 5. Distributive Law : A(B+C)=AB+AC RULES OF BOOLEAN ALGEBRA 1. A+0=A 2. X=A+1=1 3. X=A.0=0 4. X=A.1=A 5. X=A+A=A 6. X=A+A!=1 7. X=A.A=A 8. X=A.A!=0 9. A’ bar =A 10. A+AB=A 11. A+A’B=A+B 12. (A+B)(A+C)=A+BC DeMorgan's THEOREMS (A+B)!=A’B’ (AB)!=A’+B’ LOGIC GATES Boolean functions may be practically implemented by using electronic gates. Digital systems are said to be constructed by using logic gates. These gates are the AND, OR, NOT,NAND, NOR,EXOR,EXNOR gates. K-MAP The Karnaugh map provides a simple and straight-forward method of minimizing Boolean expressions. With the help of K-map, Boolean expressions having up to four and even six variables can be simplified. A Karnaugh map provides a pictorial method of grouping together expressions with common factors and therefore eliminating unwanted variables. The K-map can also be described as a special arrangement of a truth table. CMOS CIRCUIT CHARACTERIZATION CMOS is a technology for constructing integrating circuits (ICs).CMOS technology is put to use in microcontrollers, microprocessors, static RAM, and some other digital logic circuits. CMOS is an extensively used type of semiconductor. CMOS semiconductors use both NMOS and PMOS circuits. For the reason that only one of the circuit types is on at any given time, CMOS chips need less power than chips which use only one type of transistor. This makes them especially attractive for use in devices that are battery-powered, such as portable computers. There are two characterizations of CMOS: Low power consumption High noise immunity CMOS devices do not exhibit as much waste heat as other variants of logic. CMOS also grants a high density of logic functions on a chip. It was essentially for this reason that CMOS became popularly used technology to be materialized in VLSI chips. The principal difficulty in using a digital CMOS technology for analog design is that the method is optimized and distinguished for primarily one trade-off i.e. between speed and the power dissipation. Technology characterization for analog design involves a number of issues. Owing to the lack of globally applicable analog benchmarks, many test structures have to be built to suffice the needs of various systems. Op-amps, filters, comparators, data converters, oscillators, phase-locked loops, frequency synthesizers and RF trans-receivers incorporate many different functions that heavily depend on poorly modeled properties of devices. Some device characteristics, for example, capacitor mismatch and thermal noise are difficult to measure. Thus proper circuits must be involved on the die to allow reliable measurement. Some measured properties are difficult to incorporate in simulations. For example, the voltage dependence of the output impedance of transistors cannot be easily included in the simulation of an op amp. Such cases may mandate designing a complete circuit to measure the overall effect. The large number of test structures requires substantial characterization time and effort. It is therefore desirable to automate the measurements to the extent possible. The test structures together with circuits must be composed such that they can be ported into the following generation of the process with minimal modifications. Characterization for Analog Design The device and circuit properties of interest in analog design can be grouped into six categories: Dc behavior Linearity Ac behavior Matching Temperature dependence Noise Power consumption Static CMOS gates are very energy efficient because they diffuse nearly zero power when in idle. As the CMOS technology shifted below submicron levels the energy consumption per unit area of the chip increased tremendously. Power dissolution in CMOS circuits takes place because of two components: Static dissipation Dynamic dissipation Analog CMOS Besides digital applications, CMOS technology is also put to use in analog applications. For instance, there is CMOS operational amplifier ICs are within reach in the market. Transmission gates may be used as a substitute of signal relays. CMOS technology is also extensively used for RF circuits all the way to microwave frequencies, in mixed-signal applications Temperature range Conventional CMOS devices are applicable over a range of -55 degree Celsius to +125 degree Celsius. Functioning temperature near 40K have been attained using over clocked AMD Phenom II processors with a composition of liquid nitrogen and liquid helium cooling. Resistance Estimation Each layer of transistor-forming material has both a resistance and a capacitance that are fundamental components in estimating the performance of a circuit or a system. The resistance of a uniform conducting slab is R= (P/t) (I/w) Where P= resistivity, T=thickness, I= conductor length, w= conductor width Capacitance Estimation The total load capacitance on the output of a CMOS gate is the sum of Gate capacitance (of other inputs connected to the output of the logic gate) Routing capacitance (of connections between the output and other inputs) Diffusion capacitance (of the drain regions connected to the output) Power Consumption The two components of CMOS power consumption are Static dissipation Dynamic dissipation Static dissipation If the input is either at one of its steady- state logic values (0 or 1), there is no direct path from supply to ground. Thus no static power dissipates. However, some small static dissipation actually exists due to Reverse biased leakage between diffusion regions and the substrate Sub threshold conduction Dynamic dissipation It consists of short circuit power and load capacitance charging/discharging power. Short circuit dissipation is due to existence of a direct path from supply to ground when the output charges either from 1 to 0 or 0 to 1. Short circuit dissipation depends on the input rise/fall time, the load capacitance and gate design. Dynamic power dissipation can be limited by reducing supply voltage, output capacitance and the switching frequency. Electronic Data Processing (EDP) EDP indicates the use of mechanical methods to treat commercial data. Typically, this uses moderately simple, repetitious activities to process massive volumes of similar information For instance: stock updates applied to an inventory, booking and ticketing transactions to an airline’s reservation system, banking transactions applied to account as well as customer master files, billing for utility services. Data processing amenities became ready for use to smaller organization in name of the Computer Services Bureaus. Organizations used these amenities for testing programs while awaiting the arrival of their own machine. Combinational Logic In digital circuit theory, combinational logic is a kind of digital logic which is performed by Boolean circuits, in which the output is a pure function of the current input only. This is contradiction to sequential logic, where the output does not depend solely on the current input but also on the history of the input. In other terms, sequential logic has memory where as combinational logic does not. Combinational logic is put to use in computer circuits to carry out Boolean algebra on input signals and also on stored data. Effective computer circuits normally consists of a mixture of combinational as well as sequential logic. For instance, the part of an arithmetic logic unit (ALU), that does math calculations is assembled using combinational logic. Other circuits which are used in computers, such as full adders, half adders, full subtractors, half subtractors, multiplexers, demultiplexers, encoders and decoders are also built by using combinational logic. Combinational Logic analysis When logic gates are connected in unison, to produce a specified output for some specified sequence of input variables, with no storage incorporated, the resulting circuit is in the class of combinational logic. In the combinational logic, the output level is at all occasions dependent on the combination of input levels. Basic Combinational Logic Circuits 1. AND-OR Logic: In SOP form, basic combinational circuits can be directly implemented with AND-OR combinations if the complement terms are available. In general, an AND-OR circuit can have any number of and gates, each with any number of inputs, as shown below: 2. AND-OR Invert Logic: Fig: AND-OR logic diagram When the output of a SOP form is inverted, the circuit is called an AND-OR-INVERT circuit. The AOI configuration lends itself to POS implementation. The output expression can be changed to a POS expression by applying Demorgan’s theorem twice as shown below: . 3. Exclusive-OR Logic: Fig: AND-OR-Invert logic diagram The output of an Exclusive-OR gate is HIGH whenever its inputs A and B are different, its logic diagram and symbol is illustrated below: 4. Exclusive-NOR Logic: Fig: Exclusive-OR logic diagram The output of an Exclusive-NOR gate is HIGH whenever its inputs A and B are the same, its logic diagram is illustrated below: Fig: Exclusive-NOR logic diagram Universal Gates NAND gates are sometimes called universal gates because they can be used to produce the other basic Boolean functions. (a) One NAND gate used as an inverter (b) Two NAND gates used as an AND gate (c) Three NAND gates used as an OR gate (d) Four NAND gates used as a NOR gate NOR gates are also universal gates and can form all of the basic gates. (a) One NOR gate used as an inverter (b) Two NOR gates used as an OR gate (c) Three NOR gates used as AND gate (d) Four NOR gates used as a NAND gate DYNAMIC CMOS LOGIC In the context of logic design, the phrase dynamic logic is used as compared to clocked logic as it makes clear the difference between this type of design and static logic. STATIC VERSUS DYNAMIC LOGIC In the dynamic logic, a clock signal is put to use to evaluate combinational logic but in the static logic, this is not the case. Dynamic logic is twice as fast as static logic. Dynamic logic can be difficult to work with, whereas static logic is easier. Dynamic logic greatly increments the amount of transistors that are switching at given time, which also increases power consumption over static CMOS. Static Logic Example out=A Fig. CMOS NAND Dynamic Logic Example Fig. CMOS NAND SEQUENTIAL LOGIC Sequential logic is timed by clock pulses. e.g. D type flip -flop Here, in D flip-flop, on the rising edge of the clock pulse, the input D is copied to the output Q. The input at D is ignored at all times except during the rising edge of the clock pulse. SHIFT REGISTER- SERIAL DATA TO PARALLEL Once serial data has been clocked into each flip-flop, parallel data is available at the four outputs, Q0 to Q3. SHIFT REGISTER- PARALLEL DATA TO SERIAL The input data shifts one place to the right on each clock pulse and serial data emerges from the output. DATA LATCH BINARY UP COUNTER The net effect is for whole circuit to count upwards in binary. BINARY DOWN COUNTER MEMORIES Memory can be defined as a physical device which is used to store data or programs. MEMORY STRUCTURE TYPES OF MEMORY Random Access Memory (RAM) The RAM is a volatile memory, which means that we can access the information written to it as long as power is on, but it is no longer assessable when the power is off. Read Only Memory (ROM) ROM is a non-volatile memory. It is a collection of storage mechanism used in computers as well as in other electronic devices. MEMORY CELL A memory cell is the tiniest unit of information storage which holds a single 1 or 0. memory cells are classified together to form words. the position of each cell in the memory is called physical address. Some important terms defining a memory cell are given belowcapacity : number of bytes or bits that a memory can take hold of. density : capacity/size serial-access : the amount of time taken to access data depends on the physical position of the data within the memory. Access time : the time taken to read the data from a given memory location. bandwidth : the speed at which the data can be transferred from the memory to the host computer. Latency : Latency alludes to the delay between starting a memory access and the start of the transfer. Static memory : once we write the data into a static memory cell, data remains at that point until it is either modified by over-writing it with new data, or by removing the energy source if it is a volatile memory. Dynamic memory : DRAM stores data in the form of an electronic charge which resides on the 'inter-electrode capacitance' of a FET. Ideal memory has the following characteristics High speed Highly robust Small size Low cost Low power consumption MEMORY MAPPING Reset vector : The reset forces the program counter to address 0h on any given device. Interrupt vector : the program counter is forced to address 0004h when an interrupt is acknowledged. calibration information : it is stored in the program memory in some devices. program counter : the PC specifies the address of the instruction to call for execution. stack : it permits a combination of upto 8 interrupts. program memory paging : CALL and GOTO instructions have implementations. MEMORY ORGANISATION Data memory comprises of - 1. General Purpose Register (GPR) - GPR area is regulated to make an allowance for addressing the general purpose RAM greater than 96 bytes. 2. Special Function Registers (SFR) - SFRs are for the registers that keep the authority of peripheral and core functions. BANKING : The data memory is divided into four different banks. INDIRECT ADDRESSING INDF, AND FSR REGISTERS : Indirect addressing can be defined as a mode of addressing data memory in which the address of the data memory in the instruction is not settled. Any instruction using the INDF register actually gains access to register that is pointed out by FSR (File Select Register). TYPES OF SEMICONDUCTOR MEMORY TECHNOLOGIES PROM FLASH MEMORY EEPROM NOR FLASH NAND FLASH ANALOG DESIGN Some of the examples of new analog functions are MOSFETs, charge pump voltage regulators, and LED drivers. ANALOG CIRCUITS An analog circuit is one that uses consecutive time voltages and currents. P-N JUNCTION A p-n junction is the interaction of the two semiconductor materials (p-type and n-type). P-N junctions are the primary building-blocks of most of the semiconductor electronic devices such as diodes, solar cells, transistors, LEDs and ICs. In NPN, conduction through the forward biased junction is mainly by majority carrier electrons from the n-material (emitter). While, in the reverse biased junction, electrons are the minority carriers in the p-material and the holes in the n-material. Relationship Between Transistor Current Gain, Alpha And DC Current Gain, Beta DC current gain = output current/input current = Ic/Ib Again, Ie = Ib+Ic--------(KCL) and Ic/Ie = alpha Thus, Ib = Ie-Ic, or Ib = Ie- alpha.Ie, or Ib = Ie (1-alpha) Therefore, beta =Ic/Ib =Ic/Ie.(1-alpha) = alpha/(1-alpha) If now alpha= 0.99, then beta will be 99. SMALL SIGNAL ANALYSIS OF CMOS SINGLE STAGE AMPLIFIER DESIGN Single stage amplifiers such as common-source(CS), common-gate(CG), and commondrain(CD) in case of MOSFETs and common-collector(CC), common-base(CB) and commonemitter(CE) amplifiers in case of BJTs are the basic building blocks of complex analog systems. VLSI DESIGN METHODOLOGY INTRODUCTION: VLSI is an acronym which stands for ‘Very Large Scale Integration’. This is a field that involves packing more and more logic devices into smaller areas. The number of applications of integrated circuits in high performance computing, consumer electronics, telecommunication and now in the field of mechanical engineering(MEMS) has been rising steadily, and at a fast pace. The other important characteristic is that the information services tend to become more and more personalised, which means that the device must be more intelligent to answer individual demands and at the same time they must be portable to allow flexibility. DESIGN FLOW BUILDING: The design process is usually evolutionary in nature. It starts with a given set of requirements. Initial design is developed and tested against the requirements and when the requirements are not met, the design has to be improved. It is explained in terms of an Y-chart. The Y-chart mainly consists of three major domains namely: 1. Behavioral domain 2. Structural domain 3. Geometrical layout domain The design of VLSI processor may be divided in five major sections: 1. High level design 2. Operative part design 3. Control part design 4. Memory design 5. Design of miscellaneous parts. The subsequent step is the logic design of networks which constitutes of subunits and registers. When logic networks or system architecture are designed, performance as well as errors are checked with the help of CAD programs, called as ‘logic simulation’. The subject of the logic design is to decide their interconnection pattern, the overall structure of blocks, to specify the structure of data path in addition to control sequences of data path. Simulator analyses whether the network consists of hazard analysis. Logic design as well as simulation is a principal issue of VLSI CAD. LEVELS OF REPRESENTATION AND DESIGN: There are four types of logic simulators according to the levels of abstraction of simulated elements. 1. Switch 2. Gate 3. Function 4. RTL Logic networks have to be converted to electronic circuits. When the designers specify electronic circuit necessity such as power supply voltage, speed, types of logic operations, in addition to signal level tolerances, it is advisable to have CAD programs which accordingly design electronic circuits to meet all the requirements, and also specify parameters such as dimensions of transistors together with magnitudes of currents. The CAD programs normally yield the analysis of direct-current performance, transient behaviour, signal distortion, stationary alternating-current performance, noise interference, sensitivity including parameter optimization of electronic circuits. COMPLEXITY AND DESIGN: Engineering a VLSI chip is an extremely complex task. When attempting to describe the field to a no-technical group, the idea of VLSI design funnel was found. At the engineering level, digital VLSI chips are classified by the approach used to implement and build the circuit. A full custom design is one where every circuit is custom designed for the project. This is an extremely tedious and time-consuming process that makes it impractical for designing an entire system. VLSI CHIPS: Application-specific integrated circuits (ASICs) allow digital designers to create ICs. For particular applications. ASICs are very popular for prototyping or low-volume production runs. They are designed using an extensive suite of CAD tools that portray the system design in terms of standard digital logic constructs: state diagrams, function tables, and logic diagrams. Usually, an ASIC designer does not need any knowledge of the underlying electronics or the actual structure of silicon chip. Design automation CAD tools are responsible for taking the logic design and building most of the chips. One drawback of ASIC design is that all the characteristics such as speed are set by the architectural design: the designer does not have access to the electronics, so delay times cannot be changed. Modern ASICs have evolved to a high level of sophistication, and are generally capable of providing solution to a large class of problems. BASIC CONCEPTS: VLSI design is a system design discipline. Many aspects can be taught without any reference to silicon circuits. System solutions can be generated using the CAD tools, and the necessary data turned over to the manufacturing group for production. Simplifying the design processes is important. However, many of the most powerful techniques and ideas of VLSI reside at lower levels and are therefore lost. Circuits work, but they are not as fast or as small as they could have been. SCHEMATIC SIMULATION SOFTWARE INTRODUCTION: Simulation is the process of reproducing or imitating the behaviour. Simulation software can be described as, a program that give an allowance for the user to witness an operation through simulation without really performing that operation. The software is often used to design equipment so that the end product will be as close to the design specifications so as to avoid huge expenses during process modification. MOS SIMULATIONS: (MOS)Metal Oxide Semiconductor is a device in which a metallic oxide (as silicon dioxide) serves as an insulation layer. METAL OXIDE SEMICONDUCTOR FIELD EFFECT THANSISTOR: MOSFET is the common term for the Insulated Gate Field Transistor (IGFET). There are two basic forms of MOSFET: 1. Enhancement MOSFET 2. Depletion MOSFET. PRINCIPLE: By applying a transverse electric field across the insulator, which is deposited on the semiconductor material can be managed. In depletion MOSFET, the constraining electric field decreases the number of majority carriers that are available for conduction when in fact in the enhancement MOSFET, application of electric field produces an increment in majority carrier density in conducting regions of the transistor. The MOS circuits are composed of bidirectional switching elements which are connected by bidirectional wires with memory because of the interconnected devices and also device capacitances. GATE LEVEL SIMULATION: The Boolean logic gate model has performed the theoretical basis for logic design ever since the advent of electronic logic. In this model a circuit is composed of several logic gates connected by unidirectional memory less wires. A logic gate may be a simple inverter, NAND gate, NOR gate, or a more complex functional unit such as a flip-flop or a register. The logic gates compute Boolean functions of their input signals and transmit these values along wires to the inputs of other gates to which it might be connected. Each gate input has a unique signal source. Information is stored only in feedback paths of sequential circuits. SWITCH LEVEL SIMULATION: A set of digital simulators known as switch level simulators has emerged recently as an alternative to conventional gate-level simulators, especially for the MOS circuit simulations. One of the initial switch-level simulators which were implemented was the MOSSIM. And there after a large number of switch-level simulators have been implemented. CLASSIFICATION OF CIRCUIT SIMULATORS: TRADITIONAL SPICE: It uses the following techniques to ensure the typical SPICE accuracy: 1. Creating a flat net list. 2. Finding and maintaining a DC operating point. 3. Making use of globalised formatting settings. 4. Making use of original device equations. 5. Solving the full original matrix. DIGITAL FAST SPICE: Some of the techniques used by the digital simulators are: 1. They do not maintain DC operating points. 2. Makes use of simplified device models. 3. Divide up into sub-circuits and solve the matrix independently. 4. Use simulations that are event driven. 5. They use block level simulator tuning. 6. Make use of hierarchy to represent the redundant circuits. ANALOG FAST SPICE: It uses all the techniques of traditional SPICE to deliver true accuracy. These devices often provide a better accuracy when compared to the other types. SPICE simulators are those which maintain true SPICE accuracy but the performance and capacity are limited. Digital fast SPICE simulators have increased performance as well as capacity but they have to compromise with accuracy. Analog fast SPICE simulator on the other hand gives accurate waveforms to the spice noise floor 5x-10x faster, with 5x-10x higher capacity. IC LAYOUT INTRODUCTION: Integrated circuit is an arrangement of small circuits on a single chip. Silicon chip is usually preferred as it is a semiconductor. Today the integrated circuits have become an important part of most of the electronic equipments. ICs are also preferred for their low cost. ICs can be made very compact, producing up to several billion transistors and other electronic components in an area as small as the size of a fingernail. INTRODUCTION TO IC LAYOUT: IC layout is the placement of the circuits and electronic components on a chip. It is the representation of an integrated circuit in terms of geometrical shapes corresponding to the metal oxide or semiconductor layers that make up the components of the integrated circuit. The performance of an integrated circuit depends on the IC layout and hence one has to be careful with the inter-connections and the geometric shapes and their placements. A layout engineer must keep in mind the criteria like performance, size, density, and manufacturability during the process of layout of the chip. LAYOUT RULES: Design rules are essentially required to know the physical limitations of a particular manufacturing process. The design rules specify the geometric and connectivity restrictions in a semiconductor process. These rules are necessary to ensure whether or not most of the chips are working after the fabrication. The first and basic rules are the single layer rules. The width rule specifies the width of any shape in the design. The spacing rule specifies the placement of the objects keeping in mind the space between them. There are also layer two rules that specify the relationship between the two layer. CONCLUSION All the terms i.e. VLSI, VHDL AND PCB DESIGN can be better related to the process flow involved in deploying an IC(Integrated Circuit) into production environment. VLSI or very large scale integration is a technology that helps us integrate millions of transistors in one small chip. It is a structured design flow that enables millions of transistors to sit together and work on a single microchip by saving microchip area. This comes under the circuit design process flow. VHDL or VHSIC HDL or Very High Speed Integrated Circuit Hardware Description Language is a programming language that help us automate the design of ICs. It enables us to simulate our designs before actually sending it out to fabrication. REFRENCES 1. Student Reference Guide on 'VLSI, VHDL AND PCB DESIGN' by hp education academia program 2. Search Engines such as Google Chrome