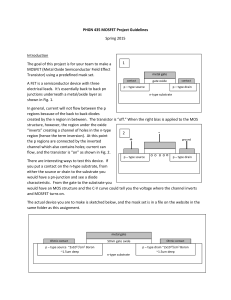

Investigation of different dielectric materials as gate insulator for

advertisement