JBB IDE-2.1

advertisement

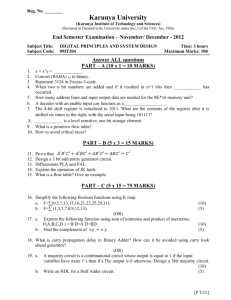

Java Bread Board Introductory Digital Electronics Exercise 2, Page 1 JBB Excercise 2 The aim of this lab is to demonstrate how basic logic gates can be used to implement simple memory functions, introduce the concept of a flip-flop and how they can be used to implement more complex components. Task 1 Place a generic 7400 NAND gate IC into the bread board. This IC contains four, two input NAND gates, for the purpose of this task we shall be using NAND gates 1 and 2, refer to JBB laboratory 1 for IC pin outs. Wire this IC to the power rails (pins 14 & 7) and its inputs / outputs as shown in figures 1 and 2. All other pins may be left unconnected. Question : start the simulation with input A = 0 and input B = 1. What is the output Y? Set input A and B = 1. Question : Pulse input B low i.e. 1 → 0 → 1, what is the output Y Question : Pulse input A low i.e. 1 → 0 → 1, what is the output Y Question : what logic function do the two NAND gates perform? o Tip, try pulsing input A or B low multiple times. Note, only one input should be low at any one time. Question : what is the output when input A and input B are connected to 0V? Figure 1: task 1 – NAND gate circuit diagram of an SR latch Figure 2: task 1 – suggested bread board layout JORUM OER PROGRAMME CONTRIBUTIONS Mike Freeman 30/04/2010 Java Bread Board Introductory Digital Electronics Exercise 2, Page 2 Figure 3: D-type flip flop waveform diagram VCC CLR2 D2 CLK2 PR2 Q2 *Q2 Inputs CLR1 D1 CLK1 PR1 Q1 *Q1 GND Outputs PR CLR CLK D Q *Q L H X X H L H L X X L H L L X X H H H H H H L H H L L H H H L X Qo * Qo Figure 4: 7474 D-type flip flop wiring diagram ____ PRE ____ CLR CLK Q _ Q D Figure 5: D-type flip flop constructed from 3 SR latches JORUM OER PROGRAMME CONTRIBUTIONS Mike Freeman 30/04/2010 Java Bread Board Introductory Digital Electronics Exercise 2, Page 3 Task 2 Place a generic 7474 D-type flip flop IC into the bread board. A D-type flip flop is an electronic circuit that can store the logic state of a single signal (called a data bit). This signal is only stored i.e. the input (D) is copied to the output (Q), on the rising edge of a clock signal input (CLK) as shown in figure 3. The output Q can also be set to a known default state (normally performed during power up) using the active low preset (PR) or clear (CLR) control lines. At all other times the output Q is fixed to the most recently stored value. This IC contains two D-type flip flops, as shown in figure 4, for the purpose of this task we shall be using DFF 1, pins 1,2,3,4,5 and 6. Wire this IC to the power rails (pins 14 & 7) and its Q output (pin 5) to an LED. The inputs to this DFF (pins 1,2,3 & 4) should be connected to +5V via a DIP switch. All other pins may be left unconnected. Note, the internal architecture of a D-type flip flop is based on a number of Set / Reset (SR) latches as shown in figure 5. Question : start the simulation with all inputs set to 1. What is the output Q? Question : Pulse the preset pin (PR, pin 4) low i.e. 1 → 0 → 1? What is the output Q? Question : Pulse the clear pin (CLR, pin 1) low i.e. 1 → 0 → 1? What is the output Q? Question Refer to figure 3 to determine what the output Q will be if the clock pin (CLK, pin 3) is pulsed low i.e. 1 → 0 → 1, then check this result on the simulator. Question : what should happen to the output if data pin (D, pin 2) is now connected to a logic 0? Check this result on the simulator. Question : what should happen if the clock pin (CLK, pin 3) is pulsed low again i.e. 1 → 0 → 1? Check this result on the simulator. Figure 6: task 2 – suggested bread board layout Task 3 Connect up the circuit shown in figure 7. Question : what will be the output signal of the D-type flip flop look like? How does it compare with the clock oscillator’s output? Confirm your answer on the simulator. JORUM OER PROGRAMME CONTRIBUTIONS Mike Freeman 30/04/2010 Java Bread Board Introductory Digital Electronics Exercise 2, Page 4 o Tip, connect LEDs to both the clock oscillator output and the D-type flip flops Q output. Figure 7: 7474 D-type flip flop driven by an oscillator Task 4 Connect up the circuit shown in figure 8. Question : what will be the output signal of the final D type flip flop look like? How does it compare with the clock oscillator’s output? Confirm your answer on the simulator. o Tip, connect LEDs to both the clock oscillator output and the D-type flip flops Q output. Question : write out the truth table for this D-type flip flop circuit i.e. outputs Output0 and Output1 for four clock pulses on the input CLK. You can assume the initial state is Output0 = Output1 = Logic 0. What function does this circuit perform? Figure 8: Two 7474 D-type flip flops driven by an oscillator Task 5 Connect up the circuit shown in figure 9. Note, inputs A and B should be connected to DIP switches. Question : start the simulation with all inputs set to 1. Pulse input A low i.e. a 1 → 0 → 1, using a DIP switch. What is the output’s state? Question : what should happen to each Q output when input A is pulsed high i.e. a 0 → 1 → 0? Confirm your answer on the simulator. JORUM OER PROGRAMME CONTRIBUTIONS Mike Freeman 30/04/2010 Java Bread Board Introductory Digital Electronics Exercise 2, Page 5 o Tip, connect LEDs to both the clock oscillator output and each D-type flip flops Q output. Question : if this circuit was used to represent a decimal number using a one-hot encoding scheme what is the maximum number it could represent? Figure 9: Four series 7474 D-type flip flops Additional Task Note, you would not be expected to do this type of logic design in an exam. Task 6 Alter the circuit shown in figure 9 to support a parallel load via a control line LD and data in lines D0 – D3. When LD is low, input A is pulsed high the circuit will behave as previously observed. However, when LD is high, input A is pulsed high the circuit will transfer the value on data in pins D0 – D3 to their associated outputs Q0 – Q3. To support these different operating mode you can use a two input multiplexer as shown in figure 10. Question : construct a two input multiplexer based on the circuit in figure 10 using only 7400 NAND gates. Confirm your solution on the simulator. Question : add a two input multiplexer to each D-type flip flops D input to achieve the desired functionality. Confirm your solution on the simulator. Figure 10: Two input multiplexer JORUM OER PROGRAMME CONTRIBUTIONS Mike Freeman 30/04/2010