ECE 527: Application Specific Integrated Circuit Development

advertisement

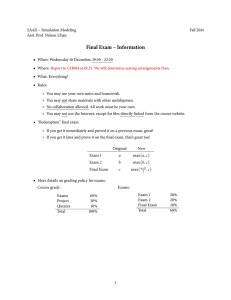

ECE 527: Application Specific Integrated Circuit Development Dr. Ronald W. Mehler Jacaranda 3303 Office hours: 2:00 – 3:00 T, Th Course web page: http://www.csun.edu/~rmehler/527s16.html Prerequisites: ECE 526/L Topics Covered 1: Synthesizable coding review. 2. Library modeling 3: Logic synthesis. Synthesis libraries, commands, constraints, scripts. Hierarchy and bottom-up methodology. Constraining designs and meeting design constraints. 4: Design issues. Clock crossings, metastability, synchronization, FIFOs. Clocks and resets. 5: Test and testability. 6: Scan and BIST. Scan insertion using automated tools. Black boxes and IP cores. 7: Static timing analysis. If time permits, other topics may include 7: Physical design, place and route 8: Design rule checking. 9: Putting the final package together for release to the foundry. Course Objectives Students should learn the tools and techniques for building reliable digital integrated circuits that meet design parameters. The lab will provide the most modern industrial design automation tools and their use will be covered in detail. Textbook None. Reference texts as indicated in lecture. Lab Manual Handouts to be provided Exams Three exams will be given (two midterm exams and one final exam). Tentative times of the midterm exams lab days in weeks seven and 12. This is subject to change. Lecture Grading Exam #1 Exam #2 Final Exam Total Lab Grading 30% 30% 40% 100% The lab grade will be the average of all labs. Letter Grades Grade A Grade AGrade B+ Grade B Grade BGrade C+ 90-100% 85-89% 82-84% 78-81% 75-77% 72-74% Grade C Grade CGrade D+ Grade D Grade DGrade F 68-71% 65-67% 60-64% 55-59% 50-54% Below 50% Academic Dishonesty Taking credit for someone else’s work is the ultimate sin in academia. Cheating and plagiarism will not be tolerated. Anyone caught cheating or plagiarizing in any form will receive a failing grade for the course and will be reported to the university for appropriate disciplinary action.