Basic BJT amplifier stages

advertisement

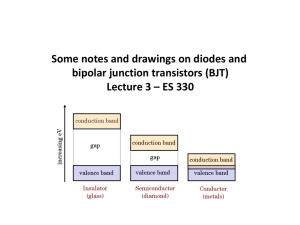

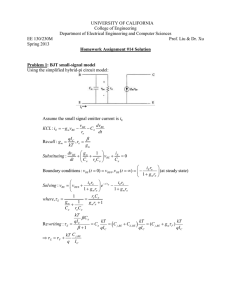

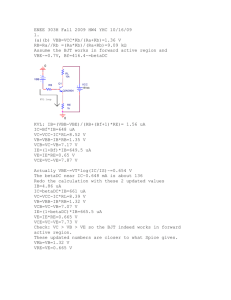

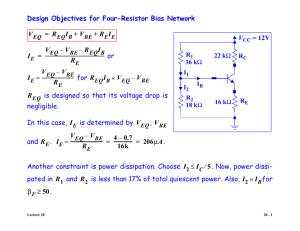

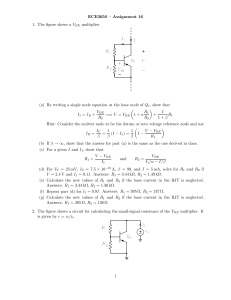

Basic BJT amplifier stages References: Sedra and Smith, Microelectronic Circuits, 6/e, Oxford P. Gray et al., Analysis and Design Of Analog Integrated Circuits, 5/e, Wiley B. Murmann, Analysis and Design of Elementary MOS Amplifier Stages, NTS Press B. Murmann, EE214B: Advanced Analog Integrated Circuits, Stanford Univ. VOUT vin VIN VOUT+ vout VIN VIN VOUT ≈ VCC/2 CE stage CE stage bias Figure 6.32 Biasing the BJT amplifier at a point Q located on the acXve-­‐mode segment of the VTC. LocaXng the Bias point Q (VBEQ) ICQ= VCEQ= Effect of Load line on allowable signal swing Small signal condiXon (1) 2 1 ! vbe $ v 1!v $ # & << be ↔ # be & << 1 ↔ vbe << 2VT 2 " VT % VT 2 " VT % 2 e vbe /VT vbe 1 " vbe % ≈ 1+ + $ ' +... VT 2 # VT & Small signal condiXon (2) iC = I S e vBE /VT = I S eVBE /VT e vbe /VT vBE = VBE + vbe For small signals (vbe << 2VT ) : e vbe /VT vbe ≅ 1+ VT iC ≅ I S e VBE /VT In pracXce: vbe ≤ 50mV/10 = 5mV " vbe % " vbe % $1+ ' = I C $1+ ' = # VT & # VT & IC = I C + vbe = I C + gm vbe = I C + ic VT vCE = VCC − RC iC ≅ VCC − RC I C − RC gm vbe (= VCE + vce ) small signal voltage gain: vce dvCE = vbe dvBE = −gm RC Q Small signal voltage gain limit cut-­‐off acXve saturaXon To maximize the voltage gain we should use a large RC à large VRC = RCIC à Low VCE à Placing the bias point Q too low leaves licle legroom for the signal to swing (BJT operates too close to saturaXon) Placing the bias point Q too high (i.e. small RC) not only reduces the gain but leaves licle headroom for the signal to swing (BJT too close to cut off) Av = − I C RC V −V R V −V V = − CC CEsat C = − CC CEsat ≤ CC VT RC VT VT VT BJT’s small signal model gm = iB = I C ∂iC = VT ∂vBE = Q ic vbe ic = gm vbe iC I C (1+ vbe / VT ) I C I C vbe v ≈ = + = I B + be = I B + ib β β β βVT rπ rπ = β VT β = I C gm β ib = β vbe = gm vbe rπ ib = vbe rπ “Extending” the small signal model IC depends not only on VBE but also on VCE iC = I S e vBE /VT ! vCE $ ∂i #1+ & → C ∂vCE " VA % ∂iC → ∂vBE ΔI C = ∂iC ∂vBE ⋅ ΔVBE + VCE=const ↔ ic = gm vbe + vce rO ∂iC ∂vCE VBE =const VCE =const ⋅ ΔVCE ↔ VBE=const ic I S eVBE /VT I C = = ≈ = ro−1 vce VA VA ic IC = = = gm vbe VT Small signal model (π-­‐hybrid model) VIN VIN VOUT VIN VOUT VIN so VOUT ? Biasing schemes • • • • Direct Biasing Biasing with emicer degeneraXon (se-­‐se FB) Self Biasing (sh-­‐sh FB) Biasing using a constant current source (replica biasing) Biasing Schemes (1) • Direct Biasing (BAD!) – Simple Biasing (fixing IB) – ResisXve Divider (fixing VBE) The very sharp relaXonship IC-­‐VBE IC = means that any small change in VBE (due to T) will result in a large change in IC (and in VCE) (b) Fixing VBE V R VBE ≈ CC B2 (I B << I R1, I R2 ) RB1 + RB2 " RB2 VCC % I C = I S exp $ ' # RB1 + RB2 VT & I IB = C β (a) Fixing IB The large variaXons in the value of β will result in large variaXons in IC (and VCE) VCC −VBE RB (Typically VCC >> VBE ) IB = IC = β I B Biasing schemes (2) • Biasing with emicer degeneraXon (series-­‐series FB) Thevenin V −V β I E = BB BE (I C = I E ≈ IE ) RB β +1 RE + β +1 To make IC≈IE insensiXve to T and β variaXons we design the circuit such that: VBB >> VBE and RE >> RB β +1 cut-­‐off Biasing schemes acXve saturaXon • Limits of the emicer degeneraXon biasing scheme There is a limit to how large we can make VBB VBB ↑ ⇔ (VRC +VCE )↓ % I R ( But ... for large gain we need large VRC ' gain ∝ C C * VT ) & ... We also need large VRC for large headroom swing (before the BJT cuts-off) But ... we need large VCE to provide a large legroom swing (before the BJT saturates) Rule of thumbs for designing an emicer degeneraXon bias circuit: VBB ≈ ⅓VCC, VCE ≈ ⅓VCC, VRC =RCIC ≈ ⅓VCC IR1≈IR2 >> IB Biasing Schemes • Biasing with emicer degeneraXon (series-­‐series FB) with two supplies Otherwise at DC the base would be floaXng Biasing schemes (3) cut-­‐off acXve saturaXon • Self Biasing (sh-­‐sh FB resistor between C and B) VB = VC − RB I B VB is always smaller than VC à the BJT is always in acXve mode (we can increase RC) " VCC −VBE RB % IE = $VCC >> VBE , RC >> ' RB β +1 # & RC + β +1 VCE = VBE + RB I B = VBE + RB IC β This scheme doesn’t offer much flexibility for the specificaXon of VCE. Typically, VCE is just a bit higher than VBE, so the collector down swing capability is more limited than with the emicer degeneraXon scheme Biasing Schemes (4) • Biasing using a constant current source Using a current source makes IE ≈ independent of β and VBE variaXons I REF = I BIAS = VCC − (−VEE ) −VBE R BIAS BIAS -VEE Figure 6.63 (a) A BJT biased using a constant-­‐current source IBIAS. (b) Circuit for implemenXng the current source IBIAS. Basic amplifying topologies The three basic configuraXons of BJT amplifier. The biasing arrangements are not shown. Common Emicer (CE) ic=βib=gmvπ Rout = vbe Av = vo −ic ⋅ ( RC || ro ) −ic ⋅ ( RC || ro ) I V = = = −gm (RC || ro ) = − C (RC || A ) ic vi vπ VT IC gm Rin = rπ = IC β VT Rout = rO = VA IC RO = RC || ro = RC || VA V RC || A IC IC β=gmrπ CE: summary • Rin=rπ=βVT/IC is moderate (to increase Rin we can lower IC, but this also lowers the gain) • Rout is moderate to high • AV can be made high (unfortunately the BW of the CE is modest) CE with degeneraXon Rout RE CE with degeneraXon: Rin Rin is boosted by (1+gmRE) TRICK vt = v1 + RE ⋅ (β +1)⋅ it vt = v1 + RE ⋅ (β +1)⋅ it vt Rin = = RE (β +1) + rπ = RE (gm ⋅ rπ +1) + rπ = rπ (1+ gm RE ) + RE ≈ rπ (1+ gm RE ) it (second pass) CE with degeneraXon: summary • The gain is less sensiXve to variaXons (β and T) • The amplifier can handle larger input signals without incurring nonlinear distorXon (vin = vbe + vE) • Rin is increased by (1+gmRE) • Rout is increased by (1+gmRE) • The high frequency response can be improved significantly for gm > 1 / RS →1+ RE < 1+ gm RE RS Bandwidth EsXmate for degenerate CE stage (3) • Another interesXng case to consider is when the Xme constant due to Cµ is negligible and RE/RS<<1: RS Cπ τ≈ 1+ gm RE • In this scenario the BW is 1+gmRE Xmes larger than in the case without degeneraXon Example + - - + + - CB stage Rout Current Buffer conXnue CB stage: AI gm ro >> 1 iout β ≈ iin β +1+ RC / r0 But … typically β >> RC/r0 so we wasted our Xme ?!? CB: summary Rin is low Rout is large CB is a current buffer (AI≈1) The voltage gain of the CB is about the same of the CE but without sign inversion (AV≈gmRC) • The CB has excellent high frequency performance • • • • CC (a.k.a. Emicer Follower) Rout e.g. Rsig Example (watch out !!) Note: v1=vπ is no longer -vt Rout vt rπ + RS = = rO || it β +1 1 RS if β >> 1 and rO >> + then : gm β Rout rπ RS 1 RS ≈ + = + β β gm β CC is not unilateral !! Emicer Follower (CC): Summary • Behavior is very similar to MOS common drain, except – We do not need to worry about backgate effect – There is finite input resistance due to rπ – The output resistance depends on Rsig (in addiXon to 1/gm) • • • • • Rin is large Rout is small CC is a voltage follower (Av≈1). CC has current gain AI = (β+1) Under the “right” condiXons the CC can work up to high frequency Discrete BJT amplifiers: CE (Blue=AC) Frequency Response of CE Discrete BJT amplifiers: CE with RE Discrete BJT amplifiers: CB Discrete BJT amplifiers: CC